Xilinx、UltraScaleアーキテクチャで大規模FPGAの配線、クロック分配を刷新

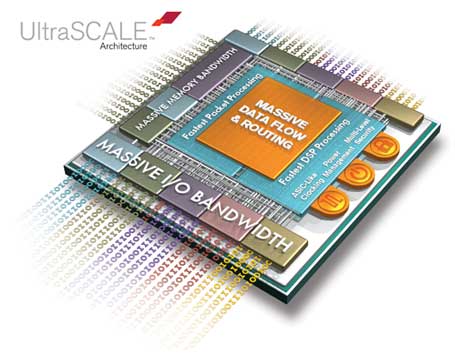

Xilinxは、20nmルールのLSIを早くもテープアウトした。デザインルールが20nmと微細化すると、集積できる回路が膨大になるため、アーキテクチャを根本的に見直し、UltraScaleと名付けた(図1)。CLB(Configurable Logic Block)周りの配線や、DSPブロック、クロック分配などを最適化した。

図1 大規模FPGA向けアーキテクチャUltraScale 出典:Xilinx

FPGAの応用製品はますます高速化、高性能化する方向に向かっている。光ファイバネットワークは100Gbpsから400Gbps、さらには1Tbpsへと向かっている。デジタルビデオは1080pのHDビデオからその4倍/2倍の4K/2K、その先には8Kへと高精細化要求も増えている。ワイヤレスネットワークは3GからLTEさらにLTE-Aへと高速のデータレートの時代へと向いている。

こういった高速・高集積のシステムをFPGAで実現するためには、FPGAだけではなく、SoCのような手法が欠かせなくなる。すなわち、CPUコアにDSPやROM、RAM、インターフェース、周辺回路、FPGAなどを集積したSoCによって大規模なLSIに対応してきた。全てFPGAで構成するならソフトウエアをゼロから開発しなければならず、もはやFPGAで出来る範囲を逸脱している。しかも大概のソフトウエアはカスタマイズされているため、再利用ができない。ここがFPGAの泣き所だ。

高集積FPGAは、性能・機能共もはやSoCというべき半導体LSIになっている。とはいえ、周辺回路に独自のハードウエア回路を集積して差別化を図ろうとする場合には、高速性能を得るためFPGA回路を利用する。このFPGA部分さえ大規模になり、配線部分がSoCの性能のボトルネックになり始めた。

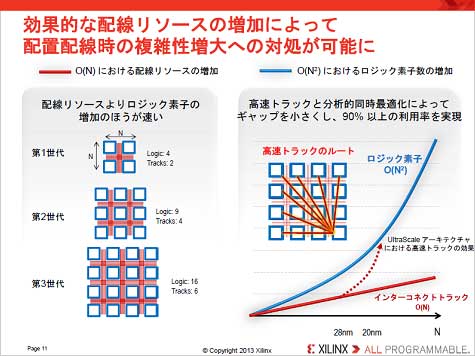

図2 多層配線で配線リソース効率を上げる 出典:Xilinx

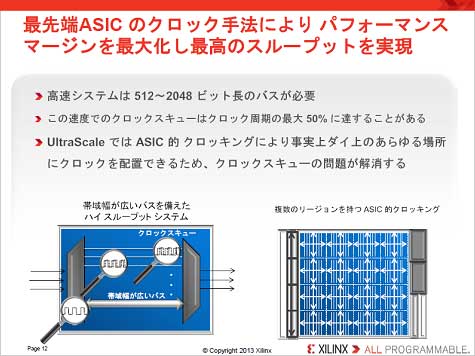

そこで、今回Xilinxは、ロジックエレメントCLBとX方向、Y方向の配線だけではスキューやジッターが増加する恐れがあるため、多層配線のリソースを斜め方向に最適化するルートも加え、配線利用率を90%以上に上げた(図2)。加えて、20nm FPGAといった高集積デバイスは、高速化のために512〜2048ビット長のバスを使うことが多い。クロックが同時に2048ビットも走るならスキューの問題が浮上してくる。このため、ASICのようにクロックツリー状にクロックドライバを導入することで例えばX方向の並列配線をドライブする場合でも、ローカルクロックのようにブロックごとに短い配線をドライブする形に変える(図3)。この結果、クロックスキューは起きにくくなる。

図3 ローカルクロックをドライブすることでスキューを防ぐ 出典:Xilinx

性能的にはDSPの計算能力を上げた。特に浮動小数点演算の場合には、単精度と倍精度の演算を可能にするため、18×27ビットのMAC(乗算累積演算器)を2個だけで54ビット幅の演算ができるようにしている。このDSPを使い、誤り訂正回路CRCやECC、EFECなどを実現している。

消費電力の削減に関しては、クロックゲーティングを用いてクロック周波数を下げるため、バッファを増やしている。また、RAMをブロックに分け、ダイナミック電力をパワーゲーティングによって、局所的に下げられるようにした。

また、複雑なSoC/FPGAをC/C++言語で設計できるようにするため、Vivado Design Suiteと呼ぶ新しい設計ツールを用意し、設計作業を早めている。新しいバージョンのVivado Design Suit 2013.1ツールにはVivado IP Integratorと呼ぶ、XilinxのIPを再利用するためのツールも含まれており、HDL言語に変換してIPもFPGA部分もRTLに合成する。

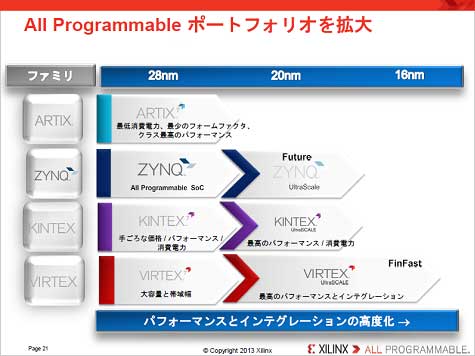

Xilinxは、今回のUltraScaleアーキテクチャを20nmデバイスから導入するが、28nmにも拡張すると同時に、16nmでも展開していく(図4)。しかも製品群についてもVirtexシリーズ、Kintexシリーズ共に導入していく。将来はZinqシリーズの製品にも適用する計画だ。UltraScaleアーキテクチャを取り込んだ最初のSoCは2013年第4四半期に出荷する予定である。

図4 Xilinx FPGA製品のロードマップ