100Gbpsシステム向けチップ設計を容易にするTabulaの仮想3次元FPGA

米国ですい星のように登場した3次元FPGAのベンチャー、Tabula社(参考資料1)がこのほどその進展状況を明らかにした。22nmのインテルのトライゲートFET技術を使う、このFPGAの具体的な製品ABAX2 Pシリーズと、ユーザーが新規開発するためのプログラムツールのStylusコンパイラを発表した。

図1 12×10Gbpsから100Gbpsへの変換ブリッジ 出典:Tabula

Tabula社の3次元FPGA技術は、小さなFPGAプレーンを用いて、さらに大きなロジックゲートの回路を時分割で消しては再構成を繰り返すものである。チップ面積が小さくなるというメリットは元々あったが、それ以上大きなメリットもある。チップ内配線遅延を抑えられるため、ロジック検証、タイミング検証を短時間で済ますことができる。性能的にも、例えばクロックを2GHzで統一的に動作させることも難しくない。チップが小さいため、レーシングやクロックスキューなどの問題も生じにくい。このため設計から検証までのタイミングクロージャが容易になり、設計期間の短縮につながる。

このチップの最初の応用は、通信基地局での100Gbpsシステムだ(図1)。従来の大規模なFPGAで100Gbpsシステムを設計することは容易ではない。チップがあまりにも大きいため、グローバル配線やローカル配線の均一性が確保できなくなり、クロックスキューやレーシングなどの問題が出てくると、クロック速度を上げることが難しくなる。このため、チップ上にクロスバースイッチ回路を集積したり、導光路を設けるシリコンフォトニクス技術を使ったりする必要があった。いずれもコストが跳ね上がる方法だ。

加えて、100Gbpsシリアル伝送の設計は難しい。「まず外部とのインタフェースをとるためのラインターミネーション(伝送線の終端)の設計が困難になるという問題がある。もちろんチップ外のDDR3メモリとのデータのやり取りを行うバスのバンド幅がボトルネックになる。オンチップメモリのバンド幅として300Gbps程度は欲しい。こういった広いバス幅を確保したとしても高性能な内部バスを扱うための信号が輻輳するバス競合の問題もある」と同社マーケティング担当バイスプレジデントのAlain Bismuth氏は言う。

図2 ABAX2 P1チップ 出典:Tabula

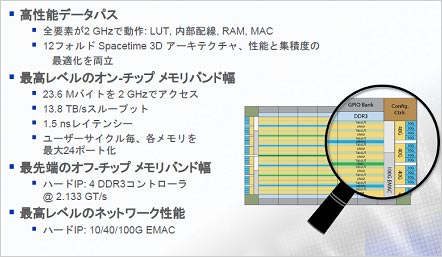

今回のABAX2 Pシリーズには、内部回路として、ロジックセルやRAM、MACブロック、配線などを設けている(図2)が、全てのコンポーネントは2GHzのクロックで安定的に動作しているという。チップ上のメモリは、12ポートと24ポートのI/O、23.3Mバイトの容量を持つ。メモリとのやり取りにおいて、13.8Tバイト/秒というスループットを実現し、複数の100Gbpsの超高速ストリームをサポートできる。時分割できる最大のレイヤー数は12層。バーチャルな3次元ICといえる。

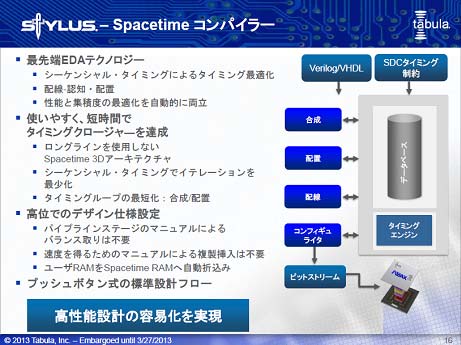

このFPGAをプログラムするための設計ツールであるStylusコンパイラ(図3)2.6では、時分割でタイミング検証するため、各層ごとにシーケンシャルなタイミングで配置・配線の最適化を検証できる。しかも長い配線を全く利用しないため、シーケンシャルなタイミング検証はわずか数回の反復でタイミングクロージャが可能になる。RTL出力から合成、配置までのタイミングループが短くて済むためだ。

図3 Stylusコンパイラでタイミングクロージャが簡単に 出典:Tabula

100Gbpsシステムのソリューションをデモするため、リファレンスデザインキットには、12×10Gbpsから100Gbpsポートへの変換ブリッジ(図1)や、4×100Gbpsのスイッチなど5例の回路を搭載している。

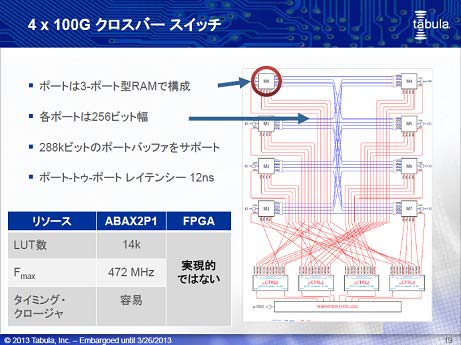

開発ツールStylusコンパイラを使って、このチップで4×100Gbpsのクロスバースイッチを設計した例(図4)がある。14k個のLUT(ルックアップテーブル)を使い、周波数472MHzで、3ポート、256ビット幅で、288KビットのバッファRAMを動かすことで、104.4Gbpsのデータレートになる。

図4 4×100Gbpsのクロスバースイッチの例

Stylusコンパイラは現在入手可能になったが、チップであるABAX2 P1は今年の第3四半期にサンプル出荷の予定である。

参考資料

1. インテルの22nmFINFETプロセスをファウンドリとして使うTabula社 (2012/03/01)