ラピダス、Esperantoとの提携で、TSMCとの違いが明確に

ラピダスがRISC-VのスタートアップEsperanto Technologiesと交わした提携は、実はここで初めてTSMCとの違いが明確に出ていた。Esperantoの会見では天才CPUデザイナーとも言われるDave Ditzel CTO(図1)も同席していたのだ。彼はかつてソフトウエアによる工夫でX86互換プロセッサを設計し、今はRISC-Vの設計を率いる。彼がTSMCとの違いを明確にした。

図1 Esperanto Technologies CTOのDave Ditzel氏

これまでのラピダスの説明では、単にTSMCと同様の先端ファウンドリを行い会社、という捉え方でしかなかった。2nmプロセスを行うファウンドリの選択肢がTSMCの他、Samsung、Intelの次にラピダスがあった。すでにラピダスが提携していたTenstorrentのCEOであるJim Keller氏とのインタビュー記事(参考資料1)では、まずGlobalFoundries、次にTSMC、Samsung、その先にラピダスで生産すると述べており、同列のファウンドリという捉え方をしている。

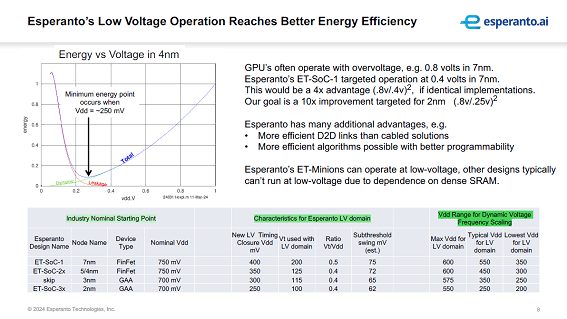

今回、Esperanto の創業者でありCTOでもあるDave Ditzel氏がラピダスを選んだのは、Esperantoが実現したい極低電圧のELV(Extreme Low Voltage)技術を共同開発してくれるからだという。Esperantoはもともと論理設計から論理合成・ネットリスト作成、配置配線の物理設計、マスク出力まで手掛けるLSI設計全てをできる会社である。つまりマスク出力までのLSI設計の全てを担ってくれる企業であり、ラピダス側はプロセスにだけ専念し、一緒に低電圧、すなわちゲートしきい電圧Vthを下げるためのプロセス技術を開発してくれるとDitzel氏は言う。Ditzel氏の考えるELV技術はプロセス技術とのイタレーションを繰り返しながら低いVthを実現する。これはTransmeta時代に取り組んできた技術(図2)だという。すなわち低VthのMOSトランジスタをラピダスは一緒に開発してくれるから、Esperantoはラピダスを選んだ。

図2 ゲートしきい電圧Vthを下げるリーク電流との最適電圧は0.25V 出典:Esperanto Technologies、Cool Chips 27 Invited Talk

TSMCやSamsungなどのファウンドリは、PDK(プロセス設計キット)と呼ばれる自らのプロセスに合ったVthのMOSトランジスタを作るプロセスしか顧客に提供しない。これに対してラピダスは顧客仕様に合わせてくれる、という訳だ。これが最も大きな違いになる。しかも、Esperantoは、設計工程の全てを担当する。

しかし、ファウンドリビジネスではLSI設計に全く興味を示さない顧客も出てくる。せいぜい論理設計でRTL(Register Transfer Level)出力まで設計してくれる顧客は多いが、物理設計まで担う顧客はほとんどいない。RTL出力からマスク出力までのLSI設計は誰が担当するのか。デザインハウスがその役割を担う。TSMCは日本のDNP(大日本印刷)やToppanなどのLSI設計を行ってマスク出力GDS-IIフォーマットまで設計してくれるデザインハウスをパートナーとして持っている。ラピダスの顧客がもっと増えると、LSI設計の素人の顧客も出てくる。

この場合をどうするのか。ラピダスの小池淳義代表取締役社長は、これからデザインハウスもパートナーとして組織化していくことを考えている、と述べた。

スタートアップのEsperantoは、創業して9年経ち、昨年ようやく製品を発表した。彼らの製品の狙いはAIサーバーを含むデータセンター。現在主流のNvidiaのGPUのアプローチではもはや消費電力で限界に来ている。最新のBlackwellスーパーチップの消費電力は2700Wすなわち2.7kWもあるという。これではデータセンターの性能は上がっても発電所を新たに設ける必要が出てくる。これはもはや許容できない。コンピューティングチップを低電圧化することはマストになってくる。

しかも性能を上げるためには高集積化は必須だが、もはやチップサイズも大きくできない。レチクルサイズで決まるからだ。しかも歩留まりは間違いなく落ちていく。そこでチップレットの登場となる。チップレットを3次元化やインターポーザ上に実装することで高集積化を達成できる。

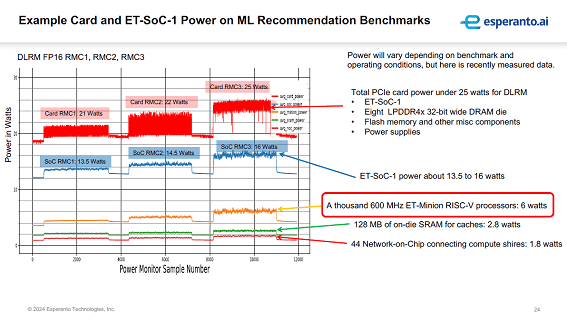

昨年製品化したEsperanto のLSI(製品名「ET-SoC-1」)のアーキテクチャでは、主に2種類の64ビットRISC-CPUコア(ET-MinionとET-Maxion)を用いる。ET-Minionは1000個ものコアを並列動作で動かし、ET-Maxionは4つのコアでアウトオブオーダー命令を実行するプロセッサだ。さらに制御用の64ビットRISC-サービスコアを持つ。命令長512ビットを持つVLIW方式をとるようだ。TSMCの7nmプロセスで製造したこのET-SoC-1チップは240億トランジスタを集積し、ダイ面積は570mm2と大きい。消費電力は15Wから60Wまで調整可能だとしている。実測データも公開している(図3)。ラピダスとの協業は、2nmプロセスを利用する第3世代のET-SoCとなる。

図3 最初の製品ET-SoC-1の実測データ、カードに実装しても消費電力は25W 出典:Esperanto Technologies

Ditzel氏は、カリフォルニア大学バークレイ校でDavid Patterson教授らと共にRISC-Vアーキテクチャを開発した経験を持つ。Esperantoを創業する前は、Transmeta社で、VLIW(Very Long Instruction Word)命令で構成され、コードモーフィング(Code Morphing)と呼ぶソフトウエアを使ってX86互換CPUを設計した。1995年創業の企業で、2000年ごろに発表したCrusouチップは日本でもてはやされた。

Ditzel氏は消費電力の少ないVLIWアーキテクチャのチップ開発、高性能・低消費電力を実現できるRISC-Vチップ開発を通して、低消費電力のAIチップを目指す。ポストGPU時代に向け、データフローコンピューティングやVLIWアーキテクチャなど新しいコンピューティング時代がやってくる、と同氏は期待する。

参考資料

1. 杉本りうこ、「『伝説のエンジニア』が明かすエヌビディアの死角」、東洋経済オンライン、(2024/03/04)