ザイリンクス、3D-IC、SoC、FPGA手法で28nmから20nmへ移行

ザイリンクスが28nmプロセスの第1世代FPGAから、20nmプロセスを利用する第2世代FPGAを積極的に進めている。第2四半期(4~6月)には早くもテープアウトする計画だ。TSMCをファウンドリとして製造を依頼し、その設計ツールを3月中には用意する。

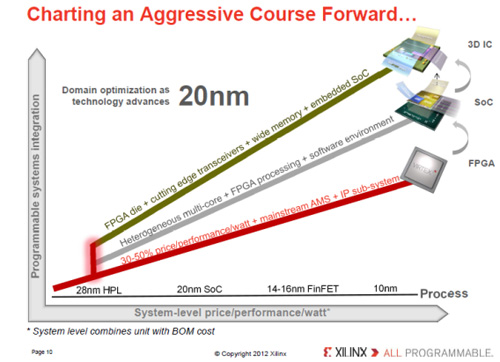

図1 28nmから始まった3種類のICは20nmでは第2世代に入る 出典:Xilinx

ザイリンクスは45nm/40nm時代あたりからTSMCとサムスンをファウンドリとして使っていたが、28nmからはTSMCに集中している。28nmではTSMCのHPLプロセスを使っていたため、生産に支障をきたさなかった。しかし28nmのLPプロセスの生産が立ち上がらなくて、クアルコムやnVidiaなどのアプリケーションプロセッサを思うように出荷できなかったという苦い経験があった。20nmへは28nmHPLが成功を収めたためにそのままスムーズに移行できると見ている。

また、ザイリンクスは28nmから始まった新しいFPGAの形態を3種類持つ(図1)。一つは、3D-IC(シリコンインターポーザを介して2.5Dとも呼ぶ)だ。二つ目は、ARMのデュアルコアとAMBAバスを使い、FPGA回路でカスタマイズするSoCである。三つ目はトランシーバ用などの従来のFPGA。これらは全て28nmを第1世代として20nmの第2世代へと移行する。

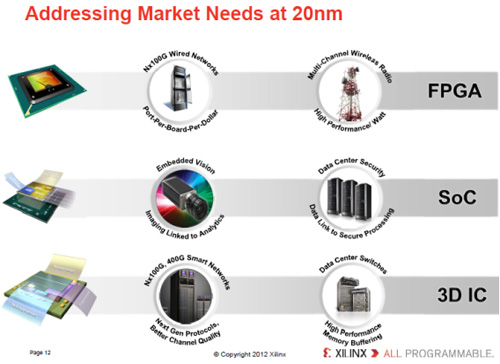

3D-ICは、メモリを並列動作させて高速のバッファリングを行う高性能はサーバーや100G/400Gbpsの幹線基地局スイッチなど、SoCはビジョンシステムや画像解析システムなどハードウエアとソフトウエアのプログラミングを行う用途を狙う。またFPGAは、LTEなどのワイヤレス通信基地局に向くと見ている(図2)。

図2 20nmチップの主な用途 出典:Xilinx

3D-ICは、現在安定して出荷しているという。平面上だがチップ間をシリコンのインターポーザを通してつなぐため、遅延が小さく、1世代先の大容量が得られるとする。これまでは同じチップを並列に接続することが多かったが、これからは違う種類のヘテロチップをシリコンインターポーザ上に形成していく。基地局のネットワークのスピードを従来の10Gbpsから40Gbpsへと進化し、今は100Gbpsシステムを開発中だという。

今のところ、完全な3次元ICという訳ではないが、コストと性能の点では二つのチップを重ねずにシリコンインターポーザの上に集積する方が有利である。コスト面やテストのしやすさなどの点で、当分この2.5次元のLSIを進化させていく。

SoCでは組み込みシステム狙いのZynqシリーズ製品がある。これはグルーロジックとCPUやメモリ、FPGAなどを1チップに集積しておき、ハードウエアのプログラムをFPGAで行う。ただし、入出力の幅がボトルネックになる可能性があり、この部分はFPGAが担当する。CPU関係をソフトウエア、FPGAをハードウエアでそれぞれプログラミングできるため、フレキシブルなチップに向く。

基地局装置に使われる高速のインターフェースはもはやASSPなどハードウエアだけでは実現できないと見る。プロセスの微細化進展が速くなると共に設計に時間がかかり過ぎるからだ。しかもLTEは各国各地域で仕様が異なり、プログラムで仕様を変える方が速い。またLTEは次のLTE-Aへ移行する場合でもプログラムでアップグレードする方が速くて簡単だ。