ARM、低消費電力化の基本を守り、製品ポートフォリオを拡大

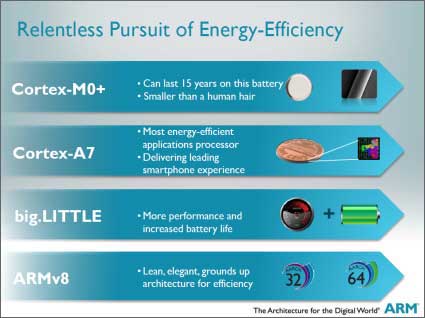

プロセッサIPベンダートップのARMが製品ポートフォリオを広げている。「一つのプロセッサでは全ての応用を最適化できない」(同社Embedded Processors担当バイスプレジデントのKeith Clarke氏)からだ。マイコン応用のCortex-Mシリーズに加え、携帯機器のアプリケーションプロセッサに向けたbig.LITTLEアーキテクチャ、サーバなどのハイエンドプロセッサCortex-A50シリーズなどへと拡張し続けている(図1)。

図1 超低消費電力から64ビットサポートのハイエンドまで 出典:ARM

これらのCPUアーキテクチャに加えて、グラフィックスであるGPU(graphic processing unit)、システムIP、フィジカルIP、ソフトウエアなどへの拡大も図っている。ただし、低消費電力にフォーカスしたIPベンダーというビジネスモデルは変えない。直接の顧客は半導体メーカーである。半導体の先にあるユーザを見据えた製品開発戦略のポリシーも揺るがない。半導体そのものが部品からシステムへと変容しているため、チップの先にある応用を見据え開発することで企業価値を高めている。いくつかの例を12月に開かれたARM Forumから紹介する。

マイコン用のコアCortex-M0+は、さらなる低消費電力を狙ったマイコンに向けたもの。CR2032のボタン電池1個で15年間動作させるという目標を設定している。この条件は、デューティ比1%、TSMCの90LPプロセス(低消費電力の90nm)で作る場合に当てはまる。この目標こそ、IOT(internet of things)への応用を狙ったものといえる。

IOTは全てのモノがインターネットでつながるという概念だ。ZigBeeなどの低消費電力プロトコルをベースとするワイヤレスセンサネットワークから進展してきている。腕時計や街灯、ソーラーシステム、自動販売機、レンタル建機、トラックやバス、照明器具などありとあらゆるモノがインターネットとつながり、それらの状態をモニターする。橋梁や火山のふもとなどにワイヤレスセンサネットワークを構築する試みはすでに行われている。防犯カメラをインターネットにつなげば、抑止力は今以上に高まる。トンネル内の天井板や壁などにセンサを付け、常時モニターするような応用も考えられている。

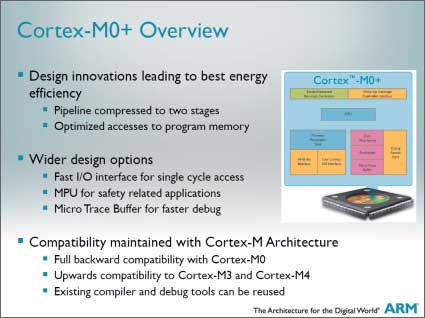

新しいCortex-M0+が狙うマイコン応用では、割り込み処理が絶えず行われ、しかもスリープ状態も多い。割り込み命令が来た後すぐにその仕事を処理できるようにするため、割り込みコントローラを充実させ(図2)、しかもパイプラインの本数を2段に減らした。パイプライン処理で長い間待たされること(レイテンシ)を防ぐためだ。加えてプログラムメモリへのアクセスも最適化している。素早く立ち上がるようにシングルサイクルで動作できる高速I/Oインターフェースも設けている。もちろん従来のCortex-M0やCortex-M3との上位互換性があり、既存のコンパイラやデバッグツールも使える。

図2 IOT向けのマイコンコアCortex-M0+ 出典:ARM

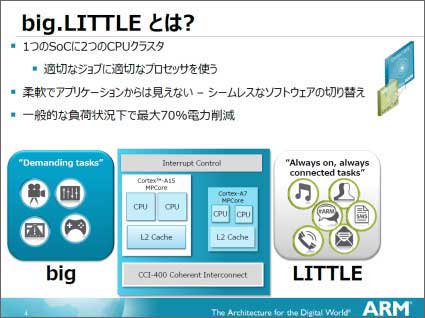

ARMの基本路線であるモバイル応用では、タブレットやスマホが低消費電力ながら高性能が求められるようになってきたため、これらをシステム的に両立させるためのbig.LITTLEアーキテクチャ(図3)の実例が出てきた。これは、高性能なCPUコアと低消費電力のコアを1チップ上に搭載し、タブレットなどの利用状態に応じてプロセッサを切り替えることで消費電力を最適化するものである。例えば、ビデオやゲーム、ブラウジングなど比較的重い処理にはハイエンドのCortex-A15デュアルコア(big)を使い、メールやSMSなど常時接続で軽い処理をするときにはCortex-A7デュアルコア(LITTLE)を使う。Cortex-A15デュアルコアは現在のスマホに入っているプロセッサの5倍の性能で、Cortex-A7デュアルコアでも現状プロセッサよりも高性能だとしている。

図3 性能を維持しながら消費電力を下げられるbig.LITTLEアーキテクチャ 出典:ARM

それぞれのデュアルコアからなるCPUクラスタにはL2キャッシュメモリを含んでおり(図3)、各CPUシングルコア同士のメモリーコヒーレンシを保っている。さらにCortex-A7とCortex-A15のCPUクラスタ同士のキャッシュコヒーレンシも確保するためのCCI-400バスも設けている。キャッシュコヒーレンシは、プロセッサが変わってもキャッシュ内容の同一性を保つための仕組みである。

スマホでウェブブラウジングをしている時に電話がかかってくるような状況は、割り込み処理が入る典型例である。このbig.LITTLEのソフトウエアでは、GIC-400割り込みコントローラによって、割り込みが入るとプロセッサ負荷に対して適切なCPUへ移行する。さらにスレッド単位で最適なCPUを割り当てるようにスケジューラが実装されている。このスケジューラは、割り込みがない場合でも負荷に応じて適切なCPUやクラスタを選択する。

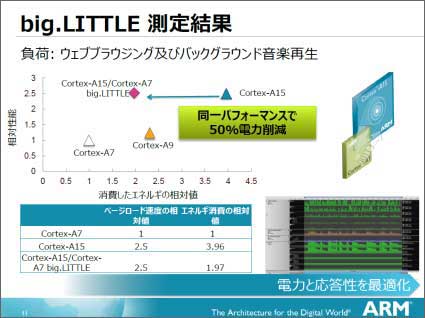

ブラウジングしながら音楽を聴くという応用では、big.LITTLEアーキテクチャはCortex-A15だけで処理する場合と比べ、同じ性能を確保しながら消費電力は半減している(図4)。

図4 big.LITTLEは同じ性能で消費電力を半減 出典:ARM

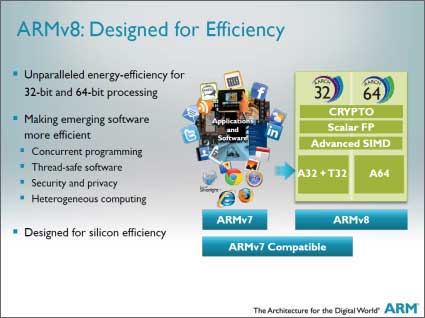

ARMはこれまで最高の性能を誇るCPUアーキテクチャARMv8についても発表した。32ビットシステムながら64ビットもサポートし、SIMD(single instruction multiple data)アーキテクチャを踏襲しながら、高速の暗号化処理、浮動小数点演算機能も搭載している(図5)。ARMv8アーキテクチャのハイエンドプロセッサの例として、Cortex-A50シリーズを11月に発表したが、このほどその詳細も明らかにした。

図5 ハイエンドのARMv8アーキテクチャ 出典:ARM

A50シリーズの最初の製品は、ハイエンドのCortex-A57とCortex-A53である。A57は、現在のスマホと同じ消費電力で性能は3倍、タブレットやノートPC向けのモバイルコンピューティング能力で5倍という。さらに64ビットをサポートし、最大16コアまで集積可能、としている。A53はCortex-A9と同じ性能で消費電力が40%ですむ、チップ面積は25%削減している(A9が32nmとしてA53は20nm)。

FINFETを利用する10nm台のプロセス技術に関しても、TSMCとは16nm、GlobalFoundriesとは14nmのFINFETプロセスを開発中だ。これによりフィジカルIP(出力がGDS IIのマスクデータ)を提供するようになる。