複数のエンジニアが同時に回路図入力できるミクストシグナル設計ツール

米メンター・グラフィックス(Mentor Graphics)社は、アナログとミクストシグナル用の設計ツールであるPyxisを発表した。これは従来同社がICStationという名称で製品化していたアナログ設計ツールを改良、回路のカスタマイズを簡単にできるようにし直観的なGUIに替えたもの。

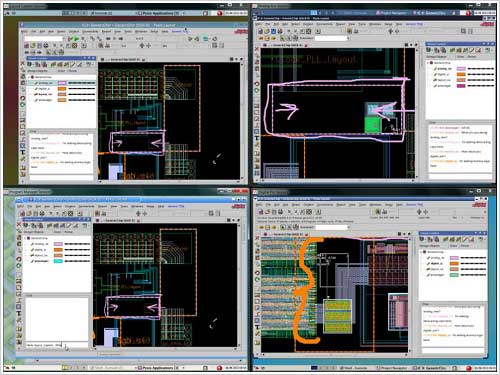

図1 Pyxis回路図入力画面 出典:Mentor Graphics

Pyxis(ピクシスと発音)は回路図入力とレイアウトやフロアプランを行うツールである。マニュアルなしで使えることを念頭に置いている、と同社Deep Submicron Division, Product marketing managerのTom Daspit氏は言う。このツールは設計回路入力とシミュレーションの設定やチェックが可能で、さらに接続性を重視したレイアウトエディターも含む。また、タイミングを考慮したラウター機能もある。

デザインスケマティック(回路図)入力画面では、優先度の高い機能を上位に表示するようにしている。電気的なルールチェックはもちろん、寄生素子を見積もることもでき、レイアウト前のシミュレーションデータから回路図やレイアウト後のSPICEシミュレーションができ、デバッグをインタラクティブに行える。

特にこのツール最大の特長は、複数の設計者が一つのセルで同時に設計できることだ。設計すべきエリアを定義して設計者同士が同じ一つのデータベース上で、それぞれ同時に設計できるため、設計時間の短縮になる。ローカル配線上でもグローバル配線上でも、自分が担当できる配線長のエリアさえ定義すれば複数のエンジニアが同時に設計できる。しかも、画面にはチャットするウィンドウもあり、設計しながらエンジニア同士で話ができる。リアルタイムで話しながら設計できるため、間違いの発生や誤解はぐっと少なくなる。

図2 自分で設計したいエリアを定義する 出典:Mentor Graphics

配置配線に関しては、トランジスタ、セル、ブロック、チップという各レベルでのアナログ回路、ミクストシグナル回路の配線を自動的に行う。配線する時の制約を設けたルールボックスによって全体的なグローバル配線では混雑を解消し、細部の配線ではネットごとに豊富な制約を設けた機構を使う。TSMCの28nmプロセス認定を受けている。

レイアウト終了後の検証では、メンターの検証ツールのCalibreがバックグラウンドで流れており、エラーを見つけるとすぐに修正できるようになっている。

このツールを使ってファウンドリへ依頼する訳だが、サポートされている多くのファウンドリを選べる上に、そのインターオペラビリティもしっかりサポートされている。台湾のTSMCやUMCはもちろん、米国のIBMやGlobalFoundries、On Semiconductor、ドイツのXFABやLFoundry、韓国のDongbu HiTekやMagnaChip、中国SMIC、イスラエルTowerJazzの各ファウンドリ企業にサポートされている。加えて、メンターのPDK(Process Design Kit)だけではなくケイデンスのPDK(ただし 変換が必要)やiPDKなどもサポートしている。デザインキットをこれから標準化するためのOpenPDKにも参加しており、メンターはその設立メンバーでもある。

ちなみにこのPyxisとは、ラテン語で海の航海に使う、「羅針盤」、ギリシャ語で「小さな箱」を意味する言葉だという。また南の星座の名前で、正式名称Pyxis Nautica(共に羅針盤の意味)と呼ぶ小さな星座もある。この星座は正式名から次第に短くなり、単にPyxisと呼ぶようになったとしている。

図3 南の空に輝く星座 この真ん中にあるのがPyxis