SpringSoft社、FPGAボード検証のデバッグ作業を可視化するツールを製品化

台湾をベースにするEDAベンダーのSpringSoft社は、FPGAでロジックを組んだ状態でRTLレベルのデバッグを早くするための検証ツール、ProtoLink Probe Visualizerを発表した。デバッグにかかる時間を半減できるとしている。

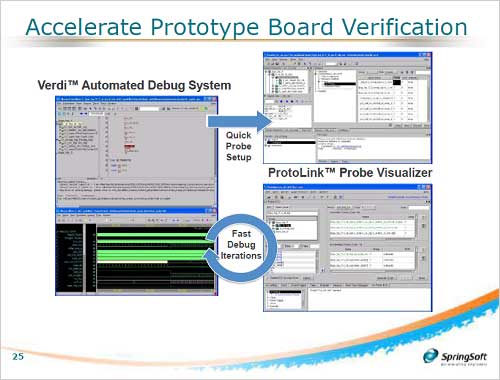

図1 RTLデバッガのVerdiと組み合わせて使いバグを可視化する 出典:SpringSoft

SoCの設計が正しく行われているかをチェックするための「検証」作業が、今やSoCの設計作業時間の半分にも達するといわれている。ソフトウエア上で検証した後もロジックが実際に動くかどうかを確かめるためにFPGAを使ってロジックを組み、そのロジックが最初の設計と合っているかどうかを確認する。このため検証作業はできるだけ早めたい。さまざまな機能検証ツールが登場してきているが、今回発表されたツールはFPGAでRTLを合成したロジックのバグをすぐにわかるように可視化するソフトウエアツールである。

同社は自動デバッグソフトウエアVerdiをすでに製品化しているが、今回のProbe Visualizerツールと組み合わせて使うことで、バグの見える化を促進する。FPGAで論理を確認するために作製するプロトタイプボードの設定に時間がかかる上、設計のデバッグ作業に必要な可視化性が乏しかった。今回のツールは、従来なら数時間かかっていた設定を数分でプローブできるとしている。

この新製品は、直観的にわかりやすいソフトウエアベースのツールであり、数100万サイクルに載った数1000もの信号を可視化できるようにしているため、FPGAベースのプロトタイプ基板のデバッグをRTLレベルに渡って見つけることができる。ここでは、RTLの論理をVerdiからドラッグ&ドロップでProbe Visualizerに持ってきて、設計のデータベースとの相関を調べる。この設計データベースには、これまでのデバッグのノウハウを蓄積しており、C言語から信号パスの状態のデータを大量に蓄積している、と同社ロジック検証グループシニアディレクタのハワード・マオ氏(図2の右)は述べる。これらのデータベースとの相関を採って信号パスを確認するだけなので、デバッグ作業は1日程度で終わるとしている。

図2 Spring Soft社シニアディレクタのHoward Mao氏(右)、COOのJohnson Teng氏(左)

このツールに付属しているProtoLink Interfaceカードには2Gバイトのメモリを搭載しており、映像情報の複数のフレーム分のデータを保存することができる上、長いサイクル数が必要なバグでさえ、簡単に把握できる。従来だとバグが見つかればRTLベレルまで立ち返って修正するため何度も検証-RTL修正を行き来しなければならなかったが、このツールだとデータベースとの間を行き来することで、やり取りの回数を大幅に減らすことができる。このようにして、合成や配置配線の間、最適化した信号を保存することができる。