ワイヤレス、低消費電力分野への注力で毎年成長してきた中小EDAベンダー

EDA業界には70〜80社が参入していると言われている。ケイデンス、シノプシス、メンターの米国ビッグ3社だけではない。時流に乗り成功している中小の2社を紹介しよう。高周波のEDAツールを狙うAWR社と、低消費電力の設計ツールに絞ったアパッチ社である。いずれも特殊なEDA製品ではあるが、成長分野に狙いを定めた製品を提供している。

図1 AWRマーケティング担当Sherry Hess氏

マイクロ波解析からノイズ解析までGUIで見やすく

AWR社が注力するのは、FM周波数から数百GHzまでの高周波領域の回路設計ツール。同社の狙いは携帯電話や携帯端末、通信技術、自動車や航空宇宙技術などこれから成長しようというワイヤレス分野である。高周波回路の設計(製品名Microwave Office)だけではなく、デジタル変調システムなどのシミュレーション(同Visual System Simulator)や、ノイズや信号処理の電磁界解析(同AXIEM)、シリコンやGaAs/GaNなど化合物半導体設計(同Analog Office)などに使うツールを製品化している。

同社は、米国ロサンジェルスにあるUCLA(University of California, Los Angels)からスピンオフし、1994年に設立され、1998年に最初の製品をリリースしたが、2010年度まで13期(年)連続右肩上がりの成長を続けてきた。「未上場の企業なので数字は言えないが、2008年ごろから黒字になり、その後は順調に利益・売り上げともにプラス成長。2011年度はすごく良い」(同社マーケティング担当VPのSherry Hess氏)と、Globalpress主催のe-Summit2011で話していたが、4月になってプレスリリースにて明らかにしたところ、2011年度(3月31日を締めとする会計年度)は対前年比30%増という結果だった。いずれ株式上場を行う。

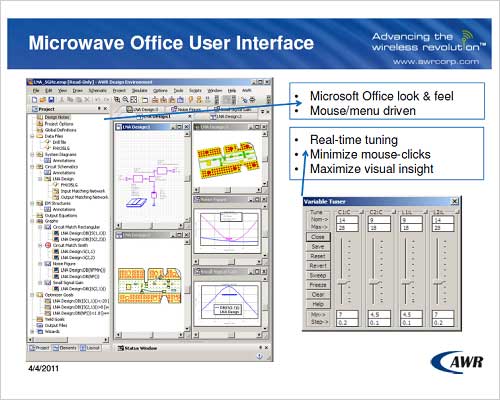

同社の強みは反射や干渉など損失の多い高周波設計において、ユーザーインターフェースにフォーカスしていることだ(図2)。マイクロソフトのオフィスと同様な見栄え(look and feel)を持つソフトMicrowave Officeを使ってパソコンベースで設計しやすいため、UNIXベースのコンピュータを使って設計する場合と比べソフトを習得する時間が半分しかかからない、とHess氏は言う。Microwave Officeは、MMIC(モノリシックマイクロ波IC)や、プリント回路基板、モジュール、SiPなどのマイクロ波回路を設計する場合に使う。

図2 Microwave Officeの回路設計画面 マイクロソフトのオフィスのような見た目

半導体デバイス、特にRF CMOSやBiCMOS、SOS、Si/Geバイポーラなどの設計にはAnalog Officeを提供している。シリコンやGaAsなどの半導体の回路設計に特化したツールであり、画面上で仮想デバイスとしての設計ができる。

同様にVisual System Simulatorは、ここのマイクロ波回路での回路図や出力波形ではなく、ワイヤレスシステムとしての、例えばデジタル変調の16QAMの状態をシミュレーションするとか、マクロ的に見て何が起きているかをチェックするのが目的だ。AXIEMはプレーナマイクロストリップラインの3次元電磁界解析設計ツールであり、渦巻状のコイルやアンテナの設計や解析、プリント基板の配線設計などに使う。

もう一つの成長軸は、オープンなデザインフローである。AWRのシミュレータや設計モデルを組み込めるように出来るだけ標準的なツールと組み合わせられるように作っている。例えば、レイアウトや回路スキマティック入力にはメンターやケイデンスのツール、回路シミュレータはシノプシスのHSPICE、検証にもメンターやケイデンスのツール、システム設計にはMATLABのモデルにも組み込める。4月にはナショナルインスツルメンツのベクトルシグナルアナライザを開発するためにMicrowave OfficeとVisual System Simulatorを組み入れた、と発表している。

日本は重要な市場と見ており、2002年にオフィスを開設して以来、グローバルなコラボレーションに力を入れている。その後韓国のソウル、2011年4月には中国の上海にもオフィスを開いた。7月にはアジア(ソウル、台北、東京)においてデザインフォーラムを開催する予定である。

アパッチ、低電力設計からEMC、ESDにも拡大

AWRがワイヤレス系に注力したのに対して、アパッチデザインソリューションズ(Apache Design Solutions)社は、もう一つの成長の軸である低消費電力ICへの応用を狙ったEDAツールベンダーだ。2001年に設立した若いベンチャー企業だが、パワー解析とノイズ解析に注力している。設立後、まだパワーが問題視されなかった180nm時代は苦労しながらも、パワーに注力してきた結果、最近の8年間は連続してプラス成長している。

同社の創立者の一人でCEOのAndrew Yang氏(図3)は、「130nm、90nm時代からパワーを考慮しなかったために設計ミスが増えてきた」と述べる。時代はデジタルチップだけではなくIPについてもパワーが不可欠な設計要素になってきた。同時に低消費電力だけではなく、最初のシリコンが設計通りに動くかどうかについてはノイズや干渉耐性、ESD(静電破壊)にもパワーそのものが影響を及ぼすようになってきたという。それもシリコンチップだけではなく、パッケージやボードレベルまで考慮に入れる必要が出てきている。

図3 Apache社CEOのAndrew Yang氏

最近では、TSVを使った3D ICなどの電力解析の要求も出てきており、消費電力と熱解析の設計手法が求められるようになってきている。そこでアパッチはパワーとノイズの問題を解くため、4つの製品プラットフォームを利用して次の3つのソリューションを言及している。

1. パワーバジェット:システムの論理設計レベルから消費電力を減らすための解析と最適化を行う

2. パワーデリバリーインテグリティ:配電が意図どおりに行われているかをチェックし、SoCの電源ノイズを解析し設計完了までサポートする

3. パワーインデューストノイズ:チップをパッケージングしボードに実装した後、チップに供給する電力が放射され戻ってくることで生じるノイズをモデル化し解析する

3D ICとしてチップとチップをTSVで接続した時の消費電力だけではなく、熱分布やストレス、それらの時間変化も解析する。さらにメタル配線内における電圧降下(エレクトロマイグレーション不良対策)についてのマップも表示する(図4)。

図4 3D ICの電圧降下分布と熱分布シミュレーション 出典:Apache Design Solutions

昨年リリースしたPathfinderソリューションは、ESD問題をチップ、パッケージから基板のRCを抽出したり、電流密度のチェックやI/Oの過渡応答をシミュレーションしたりできるようになっている。人体モデルやデバイス帯電モデルなどもサポートしている。ESDは各社各様で解決してきたが、アパッチはこれをICの安全動作領域や信頼性上の制約、熱による故障解析などを考慮に入れ、安全なESD保護できる領域を確保するような手法を開発している。

アパッチはこのほど株式上場を行うため、SEC(証券取引委員会)に届けを申請した。IPOに向けた内容については詳細を公表していないが、申請手続きはドイツ銀行証券が行うことになっている。株式公開によるキャピタルゲインで資金を調達し、さらなる成長を狙う。