メンターグラフィックス、3D IC内の各チップをテストできるツールを開発

米メンターグラフィックス社は、TSV接続を利用する3次元(3D)ICにおいてパッケージング後でもパッケージ内にある各チップをテストできるような技術戦略をGlobalpress主催のプレスセミナーe-Summit2011において明らかにした。

図1 メンターCEOのWalden Rhines氏 (左) とマーケティングディレクタのStephen Pateras氏 (右)

3次元ICは、微細化でコストダウンをしにくくなってきたことに対する解だといえる。メンターグラフィックスのCEOであるWalden Rhines氏(図1)は、これまでの微細化傾向では90nmプロセスでは前世代に比べ47%のコストダウンになったが、65nmで12%、45nmでは9%、32nmで2.5%、とコストダウンの幅が少なくなってきたと指摘した。22nmになると逆に2%のコストアップになるという。コストダウンはラーニングカーブ(習熟曲線)に沿って実現してきたが、22nmの先は技術を習熟しても微細化によるコストダウンは難しくなってきたという訳だ。3D ICがそのコストダウンの解となりうる。

3次元ICの最大の問題はコストだといわれるが、コストを決める要因のなかでも歩留まりをいかに確保するか、がさらにそのカギを握る。良品チップを3次元加工した後でも良品/不良品をテストする場合に、単に接続がうまくいっているかどうかだけではなく、例えばメモリならテストパターン通りの答えを出せるかどうかもテストしなければならない。複数のチップのテスト時間を短縮し、しかも全てのトランジスタをチェックできるようにカバー率を上げなければならない。

システムLSIの設計・検証ツールを手掛けてきたメンターは、3D ICをテストするための製品シリーズTessentを開発した。この製品を使えば、スタックされた複数のチップを階層的にスキャンし、さらにBIST(built-in self test)手法でもテストする。チップ同士をTSVでつなぐ3D ICに加え、インターポーザを介する2.5次元のICにもTessentは使える。

Tessentではまず、ロジックチップのゲート回路をできるだけ全てカバーし、しかも短時間でテストすることをメンターは考えた。カバー率の高い擬似ランダムパターンを発生するTessent LogicBISTと、テストデータをできるだけ大きく圧縮してテスト時間を短縮できるスキャンパターンを生成するTessent TestKompressを組み合わせたツールを用意した。

次に、ロジックとメモリやアナログIC、高速I/OインターフェースICなどをスタックする場合に備えて、ロジックBISTとメモリBIST、アナログテストおよびバウンダリスキャンテストを組み合わせた。これらの製品には、Tessent MemoryBISTとTessent BoundaryScan、Tessent PLLTest、Tessent SerdesTestなどがある。これらを使うことによって、テストコマンドを各チップに送り、各チップを通ってテストパターンを送り込むことができる。最大のメリットは、3D ICをパッケージングした後でさえ、チップごとにテストできることである。この階層的な手法はIEEE1149.1規格に準じている。

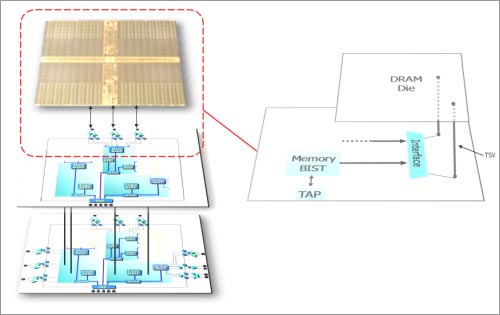

図2 ロジックに集積したメモリBISTを使いDRAMにテストパターンを送り込む

例えば、ロジックとスタックしたメモリをテストする場合には、ロジックチップに集積したメモリBIST回路を使う(図2)。この場合、3D ICのI/O端子からロジックチップのBIST回路を動かし、ATPG(自動テストパターン発生器)からメモリ用のテストパターンを送り込む。その回路からメモリのアドレスバスやデータバスをアドレッシングすることで、メモリへテストパターンを送り込むことができる、と同社シリコンテストソリューションズ部門の製品マーケティングディレクタであるStephen Pateras氏(図1右)は述べている。