顧客に加えファウンドリや同業のEDAベンダーとも組み共存を図るタナーEDA

自社開発だけで勝者になれる時代は終わった。設計だけのファブレス半導体とファウンドリの関係だけではなく、半導体メーカーとシステムメーカーの関係、ファブレス半導体とEDAベンダーの関係や、ファウンドリとEDAベンダーとの関係など、さまざまな半導体関係企業がビジネスの補完関係によりウィン-ウィンの関係を作る動きが活発になっているが、EDAベンダー同士の関係にもそのような補完関係が出てきた。

アナログ回路は全てカバーするタナーEDA

アナログやミクストシグナルのLSI設計ツールを手掛けてきたタナーEDA(Tanner EDA)は、ドイツのXファブ社やイスラエルのタワージャズ社、台湾のUMC、韓国のドンブーなどのファウンドリ企業とも手を結び、各ファウンドリのPDK(プロセスデザインキット)を提供している。ファブレスのデザインハウスやIDM半導体メーカーはもちろん顧客パートナーである。他のEDAベンダーとも手を組み、インターフェースを開発することで大手EDAベンダーともパートナーとして組む。

例えば、EDA業界の大手メンターグラフィックスの配置配線ツールのCalibreやケーデンスデザインシステムズのDraculaやAssuraとのインターフェースを備えることで共存していく。提供するソフトウエアはLinuxでもWindowsでもいずれのOSにも乗る。

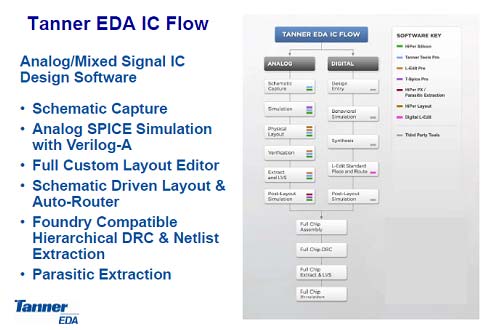

タナーのツールはアナログ回路設計なら回路図入力からシミュレーション、レイアウト、検証、寄生素子の抽出や、自動配線、レイアウトエディタ、レイアウト後のシミュレーションに至るまで全てカバーしている。このためパートナーとなっているファウンドリもアナログに強いところが多い。しかも使い勝手を良くしているため、ツールをマスターする期間が短く、ローカライズも簡単だとして、COO(コストオブオーナーシップ)が低いことが特長だと同社ワイルドワイドセールス担当バイスプレジデントのHamed Emami氏は言う。使い勝手の良さではGUIでトランジスタだけではなく、ガードバンドを入れる、アンテナ効果ダイオードを追加する、などの設定が簡単にできる。加えて、アナログのレイアウトは1回限りで使い回しができなかった。「まさにこれまではアートだった」(Emami氏)。EDS Fair 2010で発表した新しいレイアウトツールHiPer DevGen(ハイパーデブジェンと発音)は、予測可能であり、再利用可能であるため、COOが低くなるというわけだ。

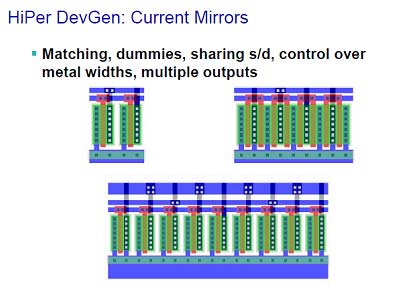

複数のトランジスタの接続情報を認識し回路情報を判断するHiPer DevGen

HiPer DevGenでは、カレントミラー回路や差動入力回路など複数のトランジスタからなる回路に威力を発揮する。従来は、こういった複数のトランジスタからなる回路を設計する場合には特別な配慮が必要で時間がかかっていた。これまでは各トランジスタを一つのデバイスとして扱ってきたためだとしている。タナーリサーチジャパンのジェネラルマネージャーである下垣佳子氏によると、今回のツールではネットリスト(回路の接続情報)を読み込むとHiPer DevGenのエンジンが、例えば二つのMOSトランジスタのソースが共通でも接地されているかいないかを認識して、差動回路やカレントミラー回路などを判断する。この情報に基づいて、隣に置くべきか、あるいはマージすべきか、ガードリングを入れるべきかなどをさらにツール側が自動的に判断するという。ガードバンドやダイオードを入れるかどうかはネットリストを設計者が設計する場合に、GUIから指定しておけばツールがネットリスト情報に基づいて解析し判断する。レイアウトツールにもGUIが表示されるのでトランジスタパターンの長さや幅などのパラメータを指定できる。

タナーEDAは、補完しあえる仲間なら誰とでも組み、さらに同業者ともパートナーシップを組み共存共栄を図っている。このビジネスモデルは半導体メーカーにも当てはまる。システムLSIあるいはSoCがあまりにも複雑になってきたため、自社は得意分野に集中し不得意分野(自社の弱み)をコラボレーションによってカバーすることで、半導体ビジネスを成長させることが世界の潮流になっている。IBMのコラボレーションアライアンスしかり、SEMATECHの低コスト技術開発しかり、半導体各社の共同開発しかりで、相手と補完し合うことでウィン-ウィンの関係を築けるかどうかで、半導体ビジネスの勝者が決まる。