ケイデンス、SoC設計期間の遅れにより大幅なコスト増を指摘、解決策を提案

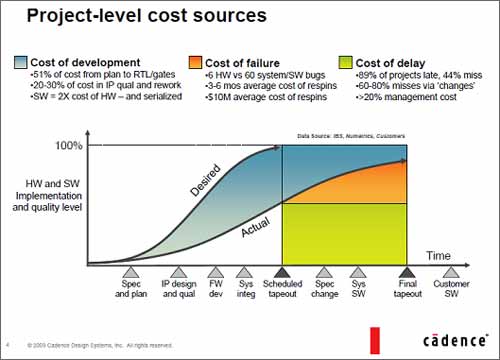

SoCのコストを削減するため、ケイデンス・デザイン・システムズ社が主催した「DA Show CDNLive! Japan 2009」において、同社バイスプレジデントのSteve Glaser氏はIPの再利用とその検証性、高い抽象性が開発期間の短縮に効果的と力説した。さらに市場への投入が遅れるとコストが上がることを示し、期間短縮がいかに重要かについて述べた。

複雑なSoCを設計する上でIPの利用と、TLM(トランザクションレベルモデリング)などの抽象化は欠かせない。SoCには、ユーザーの要求する低いコストと差別化戦略に合わせて、50〜100個ものさまざまなIPを1チップに集積する。この場合、アナログやデジタル、ソフトウエアのIPを集積するときのボトルネックがどこになるのかを探し、ユーザーの要求とIPとの関係を引き出す。

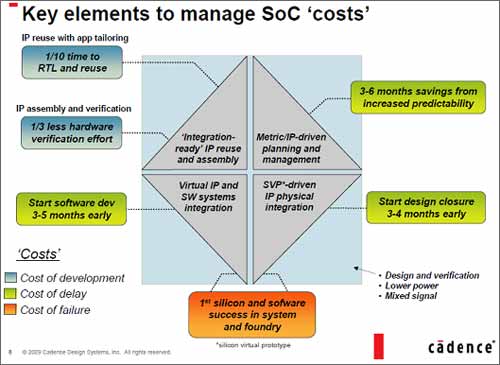

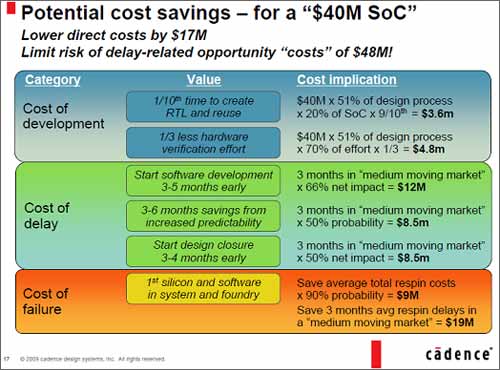

既存のIPを新しい応用に合わせて調整し再利用できるようにするためには、Verilogなどを使ってRTLを書くのではなく、高位合成向けにはSystemC、アルゴリズムを計算するためのプログラムはC/C++で書く、というような抽象レベルの高いESL設計を行う。これによってコード行数は減り、デバッグも少なくできるため、再利用できるように調整するための時間は1/10に減らせるという。

加えて、新しいSoCアーキテクチャ、IP評価、IPの集積化する場合のミスを防ぐため、その実装状態を自動で見ることのできる検証ツールを使い、実装(集積化)する時間を従来の1/3の時間に短縮する。

SoC全体の設計は3〜4ヵ月短くできる。ここでSoCの消費電力や集積化するときの制約条件などを見積もり、解析する。TLMとRTL物理合成によって物理設計を済ませ、IPの物理集積、SoCのバスや消費電力、クロック遅延などを見積もり、早期にフィードバックをかけることで実際の値との差を減らしていく。FPGAなどのシリコンプロトタイピングも利用してハードウエアの検証を行う。

ソフトウエア開発はSoC全体設計とほぼ同時に始めることでソフトウエア開発期間を3〜5カ月短縮できる。ここでは、プロセッサモデルや仮想的なIPを作りソフトウエアシステムを搭載することを想定して開発を進める。ここでもTLMベースの独自IPと、SystemCを実行できるシミュレータを活用する。

最初のシリコンで完全動作を実現するためには、設計→実装→シリコンプロトタイピング→評価、の繰り返しを十分に行い定性的な予測を出来るだけつぶしていく。定量的な評価を行うことで3〜6ヵ月節約できるとしている。

こういった手法を使うことで、開発コストの削減、開発期間の短縮、1発完動が可能になるとして、4000万ドルのSoCを開発するのに、最大6500万ドルのコスト増がありうると指摘した。その内、直接のコストとして1700万ドル、遅れによるミスや作り直しなどのリスクで生じるコストが4800万ドルと見積もっている。