メンター、SoCのデータパス系だけではなくコントロール系にもC言語設計を拡張

メンター・グラフィックスは、C言語によるLSI設計手法や検証を、従来のデータパス系回路だけではなく、コントロール系回路にも適用できるようにCatapult C Synthesisを拡張、これによりフルチップの高位合成ができるようになった。極めて複雑なデジタルLSI、SoCを開発する上で、RTL作成までの工数が短くなり、また設計データを再利用しやすくなる。

データパスは、デジタルロジック回路の中で加算やロード/ストアなどの演算処理を行うデータ経路であり、コントロール回路は命令に従って何をどうするべきか、メモリーやデータパスに指令を出す回路である。デジタル回路のシーケンスに沿って演算するのはプログラムによって手順をしっかり書けば演算できるため、データパス回路のC言語サポートは可能だった。しかし、バスにおいてデータが競合するときの判断や、優先順位の決定などのコントロール回路ではC言語設計はこれまでできなかった。コントロール回路では、明示的モデルによる調停が必要であり、データの欠落や無視することも起きる。データがない場合でもジョブを実行したり更新したりしなければならない。このため特化した言語が必要とされていた。

SoCの中のプロセッサコアはARMやMIPS、SH、Vシリーズ、PowerPCなどをコアとして使えば事足りるが、周辺回路や通信バス制御など複雑になってきたコントロールロジック回路では、設計が複雑になりC言語からRTLを自動生成する高位合成技術が望まれていた。直接RTLを求める手法ではタイミングを考慮した設計や検証に時間がかかる上に、設計に混入するバグも多くなる。RTLの検証には前後の工程を行ったり来たりする回数が増え、時間がかかっていた。少しでもバグ減らすためにも設計の抽象度を上げてC言語を利用する方法が求められ、ESL(electronic system level)と呼ばれるC言語設計がもてはやされてきた。

ESLを使えば、抽象度が高まり、コーディングを少なくできるため、設計時間も検証時間も短くなる。このような高集積なSoCは通信インフラ機器や画像処理、宇宙航空機器などの応用に使われている。

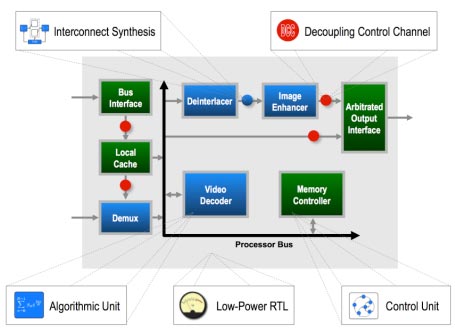

これまでのメンターのESLツールであるCatapult C Synthesisでは、内部ブロックの制御、複数ブロックのデータフロー制御に関してはC言語設計が出来ていた。今回、Catapult C Synthesisの拡張によって、クロックで信号を制御する同期式を使いながら外部ブロックまでも制御するようにC言語(C++ソース)で明示的に定義できるようになった。アービターを使ってジョブの優先順位をつける場合、データを取りに行くのか待たせるのかを判断するなど、クロック関係を表現できるとメンターは言う。具体的にC++ソースをどう表現するのかについては言及しないが、同期制御可能なC++の仕組みを提供する、とメンター・グラフィックス・ジャパンのテクニカル・セールス本部シニアアプリケーションエンジニアの渡邉智昭氏は述べる。

同期制御可能なC++の仕組みについて具体的な詳細について触れないが、制御チャンネルを分岐すること、さらにクロックによるコントロールユニットと、データによるアルゴリズム処理とのインターフェースを導入、合成する、としている。

C言語記述からRTLを合成するだけではなく、検証やデバッグもできるような環境を作った。生成されたRTLを検証する。RTL動作とC++ソースのバックアノテートを行い、ソースコードのデバッグを行う。

今回、コントロール回路までC言語設計ができるようになったことで、フルチップの高位合成が可能になるだけではなく、低消費電力設計もできるようになる。具体的にはクロックゲーティングの挿入可能な場所を自動的に見つけられるため、手修正が不要になる。また、回路ブロックの動作状態を把握し、どの回路が止まっているかを通知するためのフラグを合成することもできる。

メンターは、このツールの拡張版を大手半導体メーカーに実証してもらっており、製品としての一般市場への提供は年内までに行う予定になっている。