NECエレ、賢い90nmCMOSで2.7Gsps/50mWのフラッシュA-Dコンバータ実現

微細化するとバラつきが増え、アナログ回路を作りにくくなる状況を打破するようなA-Dコンバータ回路アーキテクチャをNECエレクトロニクスが開発、VLSI Symposiumで発表する。この技術を90nmCMOSアナログプロセスに適用、変換速度2.7Gサンプル/秒と高速ながら消費電力が50mWと少ない6ビットのフラッシュ方式A-Dコンバータを試作した。抵抗のトリミングは全く使っていないため、生産性が高い。

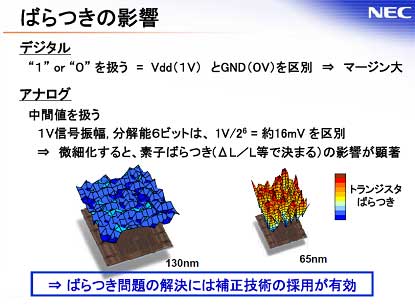

CMOSトランジスタを微細化していくにつれ、ゲート長などのバラつきがVthのバラつきといった電流・電圧値に大きく影響を及ぼす。デジタル回路とは違い、同じ程度のバラつきでもアナログ回路の微細化には限りがあった。もちろん、マスク上で補正することは常識ではあるが、それだけではデジタル回路と同じ程度のバラつきならアナログ回路は動作しにくくなってしまう。NECエレは今回、特性バラつきを打ち消し合うようなA-Dコンバータの新しい回路方式を考案した。

ビデオや映像応用のA-Dコンバータでは、フラッシュ方式と呼ばれる並列方式を使うことが多い。この方式は、下位ビットから上位ビットにかけて、分解能に応じてコンパレータをずらっと並べ、一度に比較していく方式を使うため、高速のコンバータによく使われる。今回のように分解能が6ビットであれば2の6乗すなわち64個のコンバータを並べる。

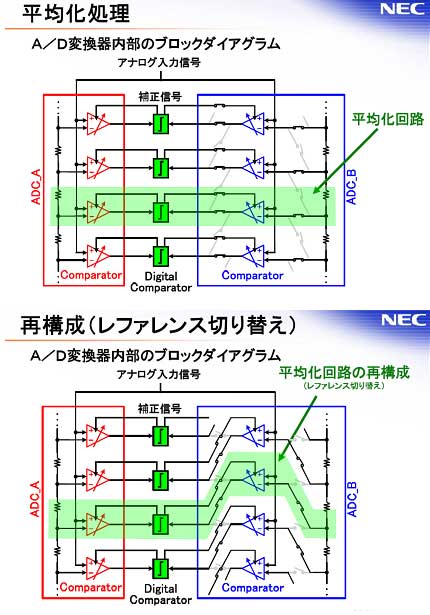

コンパレータには高精度の基準電圧源が必要になるが、これが素子バラつきに影響される。そこでNECエレが考えたのは、1ビットのA-Dコンバータすなわちコンパレータを、1/64Vcc電圧単位で2個ずつペアにして配置し、それぞれの差分を採り平均化する方法である。差分はデジタルコンパレータで比較し、もし差分が大きすぎるなら隣のコンパレータに切り替え、再構成し直す。すなわち、ペアのコンパレータの平均と再構成(補正)という考え方でばらつきを減らすという訳だ。

今回の回路ではコンパレータを65個設置した。コンパレータを切り替えて再構成し直す考え方はメモリーの冗長構成(リダンダンシ)に似ている。ペアのコンパレータが冗長に1対用意されているようなもの。

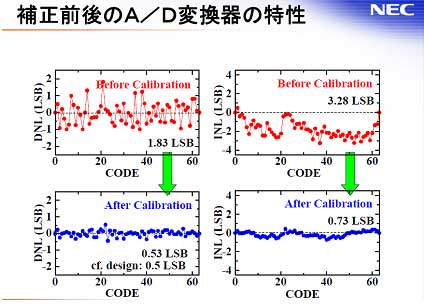

NECエレは補正する前と後でのA-Dコンバータの特性を比較している。バラつき誤差DNL(differential non-linearity error)が補正前は1.83LSB(least significant bit)と大きかったが、補正後は0.53LSBと使えるレベルに収まった。また非直線性誤差INL(integral non-linearity error)は補正前が3.28LSBと使い物にならないほど大きかったが、補正後は0.73LSBとまずまずのレベルに収まっている。

従来のフラッシュコンバータだと抵抗のトリミングをしながらバラつきを抑えていくという方式を使うことが多かった。しかも基準電圧源は高精度が要求される。このため、低コスト化できなかった。今回の技術はトリミングの必要がなく、低コスト化しやすく競争力があり、生産性が高い。微細化による低消費電力という点も大きい。

90nmプロセスで作ったこの6ビット回路のチップサイズは0.36平方mmと小さくできた。ちなみにISSCC2009ではIntelがカーネギーメロン大学と共同で、45nmCMOSで作った7ビットA-Dコンバータのチップ面積は1平方mmもあった。NECエレの回路で7ビットに拡張するならコンパレータの数が2倍増えるため単純にチップ面積も2倍になると仮定しても0.72平方mmにとどまる。