小型、低消費電力のFD-SOIによる10万ゲートのFPGAをLatticeが出荷

10万ゲートの中規模FPGAながら、パッケージ面積が81mm2しかない製品「CertusPro-NX」をLattice Semiconductorがサンプル出荷を開始した。Samsungの28nm FD-SOI(Fully Depleted Silicon on Insulator)プロセスを使っているため、SRAMベースのFPGAながらソフトエラー率が1/100 FITとかなり小さい。

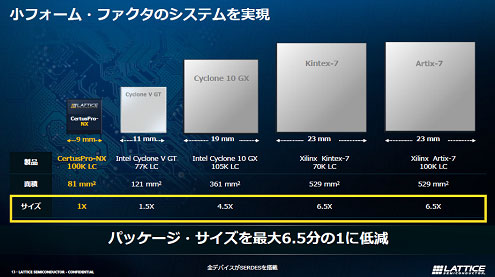

図1 フォームファクタがとにかく小さいFPGA 出典:Lattice Semiconductor

XilinxやIntel(旧Altera)が大規模を追求するFPGAに対して、小中規模のFPGAで勝負するLatticeは、これまでのコンペティタの提供する製品よりも圧倒的に小さい製品(図1)を出した。FPGAはハードウエアで組むロジックをやたらと大きくするにはもはや無理が出てきている。XilinxやIntelは大規模化に対して、FPGA回路を集積しながらCPUやメモリも搭載してソフトウエアでカスタマイズする部分とハードウエアでカスタマイズするFPGAの両方を集積したSoCを提供してきている。

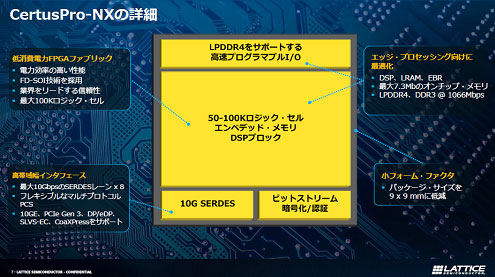

これに対してLatticeは、FPGAを中心としながらもホストCPUへのつなぎとなる広帯域幅インターフェイスのSERDES(直列並列変換)専用回路を集積し、10GbpsのPCIeをサポートしている(図2)。SERDESは、マルチプロトコルをプログラムできるようになっている。システムの高速化を支援するためにLPDDR4をサポートする高速のプログラマブルI/Oも集積している。さらにプログラマブルなロジック部分には最大7.3MビットのSRAMを集積し、レイテンシの短いデータ処理、特にAI処理を可能としている。

図2 50k〜100kのロジックセルに加えて、ホストとの通信に10GbpsのPCIeに加え、エッジ処理向けの高速I/O、さらにAI処理用のDSPとEBRバッファメモリ、最大7.3Mビットメモリを集積している 出典:Lattice Semiconductor

また、自動車や産業用、通信インフラ向けなどミッションクリティカルな応用に向け、アルファ線によるソフトエラー率(SER)を調べた。アルファ線をFPGAデバイスに2時間照射し続け、そのSERを競合他社2社と共にテストした。競合2社は、ソフトエラーを起した回数は290回、107回と共に100回を超えたが、Latticeの新製品はゼロであった。更なるテストによって、Latticeは1/100 FITという低いSERを求めている。このFIT(Failure in Time)という数字は、10の9乗(10億)の部品・時間当たりの故障率を表す単位で、例えば部品1000個を100万時間テストして不良が1個出る場合を1FITと定義している。

LatticeのSRAMベースのFPGAのアルファ線による故障率が低いのは、SOI技術を使ったためである。FinFETだとバルクを使うため、電圧による空乏層が三方向に出来る。このため、放射線などによる電子-正孔対が生まれてビット反転を起こす可能性が高いが、SOIは下地が酸化膜なので空乏層は広がらず、電子-正孔対が発生する可能性は低い。SERが低いことは、FD-SOIの最大のメリットともいえる。

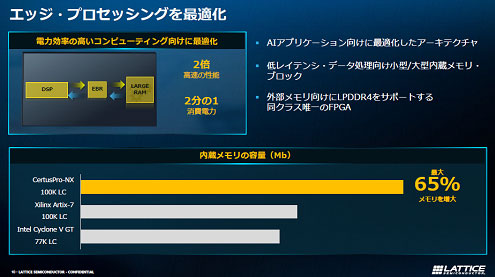

機能としては、AI用に最適化したアーキテクチャを揃えた(図3)。MAC演算専用のDSPブロックに加え、バッファメモリEBR(Embedded Block RAM)と、最大7.3Mビットの大容量メモリを備えており、機械学習やディープラーニング処理を行うのに向いている。さらに外部の大容量高速メモリLPDDR4をサポートするプログラム可能なインターフェイスを設けた。

図3 AIなどエッジ処理に適したアーキテクチャで高速・低消費電力を狙う 出典:Lattice Semiconductor

応用として、屋外の通信基地局や自動車、工業用、防衛などを想定しており、-40〜+125°Cの使用温度範囲に対応する。これらを想定して、AIやマシンビジョン、自動車などの応用を促進するため、各種のソフトウエアスタックも用意している。AIにはSensAIソフトウエアスタックでAIソリューションの実装を促進する。マシンビジョンや自動運転車に向けたADAS、ビデオ監視などにはmVisionソフトウエアスタックを揃えている。そして、Industry 4.0や自動化のためのソフトウエアツールAutomateを使って、予知保全機能を備えたマルチチャンネルモータ制御やインテリジェントな産業システムを構築しやすくしているという。