Xilinx、NoC配線技術とヘテロプロセッサで電力効率の良いSoCを開発

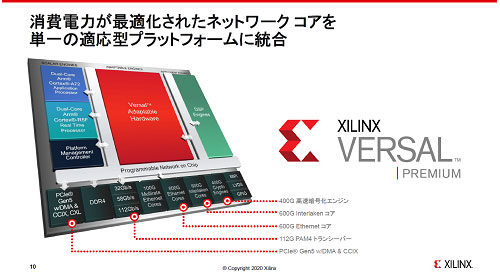

XilinxはFPGAによるダイナミックに再構成可能なハードウエア回路からCPUによるソフトウエア部品、さらにはAI機能までも搭載したACAP(Adaptive Compute Acceleration Platform)プラットフォームを発表して以来、その製品としてVersalシリーズを次々と出している。このほどVersalプレミアムと呼ぶセキュアな高速ネットワークに向けた製品(図1)を発表した。

図1 ネットワークスイッチ機能を強化したVersal Premium 出典:Xilinx

このSoCの狙いは、データセンターやコア基地局のように、シリアルデータを高速に切り替えられ、しかもセキュアにしたこと。5G時代になると、誰でも気軽にスマホからビデオ映像をダウンロードだけではなくアップロードするため、基地局ではそのトラフィックが大きく増えるためシリアルデータを高速スイッチングしなければならない。これまでの100Gbpsではコア基地局では対応できなくなる。このため400Gbpsへの準備が現実的になる。さらにその先には800Gbpsが迫られる(図2)。

図2 セルラーネットワークの基地局として、アクセス系からコア基地局まで全てのレイヤーをカバーできる 出典:Xilinx

新製品Versalプレミアムの特長は、コネクティビティとセキュリティコアを集積してネットワーク機能を強化したことである。光ファイバからのデータもサポートしており、CPUとFPGA、DSPをそれぞれ集積している。それぞれが3つのエンジンと呼ぶ機能を担当している。

CPUを中心にした演算・制御のソフトウエアで処理するスカラエンジン(図1の左上)、FPGAで好きなハードウエア回路を構成できるアダプタブルエンジン(図1の真ん中の赤い部分)、そしてDSPは演算ビット幅をスライスした単精度とミクス精度のインテリジェントエンジン(図1の薄緑の部分)、という3種類のエンジンを集積している。

DSPは元々、MAC(積和演算)専用のマイクロプロセッサである。従来は演算精度を上げるため、単精度(32ビット)から倍精度(64ビット)に細かくし、しかも浮動小数演算を行えるようにしていた。今回は機械学習のMACを並列に多数並べており、整数演算だけで、8ビット、16ビット、32ビットとミックスの精度を用意した。

これら3種類の主要コアに加え、高速のSerDes(シリアライザ/デシリアライザ)としてのシリアルインターフェイスである600GbpsのInterlakenコア、600GbpsのEthernetコア、112GbpsのPAM4トランシーバ、PCIeのGen5(DMA付き)などハードワイヤード回路を集積した。

今回の重要な技術は、NoC(Network on Chip)技術であり、NoCで全てのエンジンをつなぎ通信できるようにしたことだ。キャッシュメモリを各コアで共有するためのコヒーレンシも備えている。加えて、入出力インターフェースからデータを暗号化して出力するための400Gbpsの高速暗号化エンジンも集積し、送るべきデータのセキュリティを上げた。

従来のFPGAでは、ロジックとラウティング(配線接続)に20万LUT(Look-up Table)を使っていた。今回はLUTを使わずにインターフェース回路をハードワイヤード化したことに加え、NOCスイッチ技術によって、無駄な電力を落とした。これによって、Xilinx社のこれまでの製品16nmのVirtex Ultrascale+2個組と比べ、40%の消費電力で800GbpsのDCIスループットを実現できた。

図3 各種AIに対してメモリ帯域幅が広がり高速に 出典:Xilinx

またAI機能を実行する場合でも、従来のGPUやCPUでの演算よりも速い(図3)。ResNet50で224×224の画像認識・分類では、GPUの1.6倍〜2.3倍、Yolov2(608×608)の物体検知ではGPUの4.6倍〜7.7倍、高速になった。また、異常検知に使われるAI(Random Forest)ではIntelのXeonの65倍という結果を得ている。

製品シリーズは、システムロジックセルが1.6MのVP1102から同7.4MのVP1082まで揃えている。それによってSoCパッケージサイズが35 mm×35mmと、4つのシリコンチップを搭載している65mm×65mmがある。パッケージングには、TSMCのSSIT(Stacked Silicon Interconnect Technology)とCoWoS(Chip on Wafer on Silicon)技術を使ったとビデオ会見で述べている。

Xilinxは、CPUソフトウエア開発とAIライブラリや開発環境(CaffeやTensorFlow、PyTorch)を統合したVitis開発キットをすでに提供しており、ハードウエア評価キットも20年後半に提供する計画だ。