Altera、14nm FinFETプロセスのStratix 10技術を明らかに

Alteraの最新FPGA/SoCである、Stratix 10の技術と実性能が明らかになった。AlteraはStratix 10を2013年10月にリリースしていたが、このほどその性能の実力値とその裏付けとなる技術について発表した。

図1 Stratix 10の性能と裏付けるテクノロジー 出典:Altera

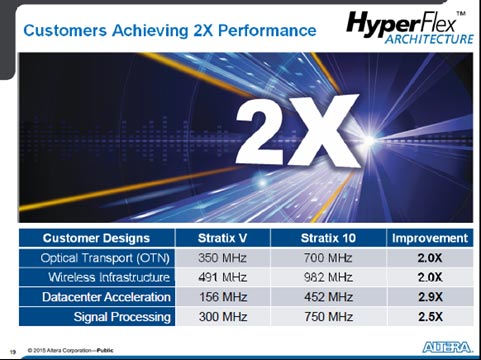

Stratix 10は14nm FinFETプロセスで製造されるFPGA & SoC。Intelがファウンドリになっている。現世代のStratix 5と比べて、コアの性能は2倍以上であることを光トランシーバやワイヤレス基地局、データセンターのアクセラレータ、信号処理などの応用で実証した(図2)。コアの性能だけではなく、消費電力は最大で70%も削減し、セキュリティも確立した。浮動小数点演算性能は最大10TFLOPS、とGPU(グラフィックプロセッサ)並みを実現している。

図2 性能は2倍以上 出典:Altera

これらの性能を実現するため、Intelの14nm FinFETに加え、2.5次元IC技術も利用、さらにクリティカルパスにレジスタを設け、パイプライン的にデータを転送させるHyperFlexアーキテクチャを採用した。

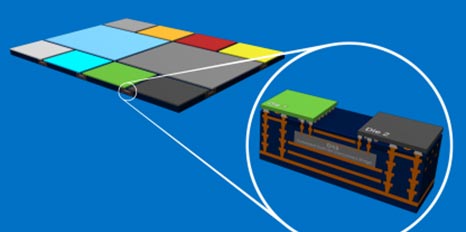

Intelの2.5次元ICは、従来の2.5D ICとは違い、TSVを使わずに平面上にチップを並べるSiP(Silicon in Package)である。従来の2.5Dだと、シリコンインタポーザの上にSoCやメモリ、FPGAなど複数のチップを集積し、インタポーザの配線にTSVを駆使した(例えば、Xilinx;参考資料1)。

AlteraはこのSiP技術を、ヘテロジニアス3D SiPインテグレーションと呼び、64ビットのマイクロプロセッサARM Cortex-A53コアを内蔵したSoCにメモリやFPGAなどを集積している。Intelは従来のシリコンインタポーザやTSVを使わないこの2.5D技術をEMIB(Embedded Multi-die Interconnect Bridge)と呼ぶ(参考資料2)。EMIBでは、シリコンインタポーザに相当するチップをぐっと小さくし、二つのチップ同士をつなぐための配線チップとして、プリント配線基板に埋め込んでいる(図3)。いわば基板内蔵チップ技術である。このメリットは、配線用チップが小さく、TSVも使わないため、低コストで製造できること。ただし、チップを3個集積する場合には、第3のチップと接続するための配線用チップをさらに基板に埋め込む。

図3 IntelのEMIB技術 チップ同士をつなぐ配線チップを基板に埋め込む 出典:Intel

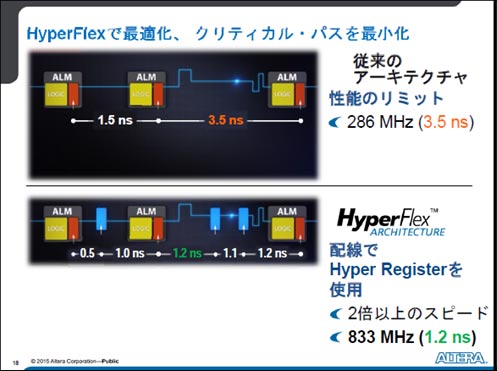

HyperFlexアーキテクチャは、配線遅延を減らすための技術である。14nm FinFET技術ではトランジスタの性能は上がるものの、配線を微細化できず配線遅延は大きく減らない。14nmプロセスでは、配線遅延がチップ全体の遅延の7〜8割を占めるため、この部分を高速化することが14nm LSIの高速化につながる。そこで、性能を支配するクリティカルパスを明らかにし、その部分にレジスタを配置して、パイプライン動作をさせることで、実質的に配線遅延を分割した。

例えば、図4のように、ロジック回路からロジック回路まで、従来の技術なら最長3.5nsかかるが、このHyperFlexでは途中にレジスタを入れて、遅延を分解する。HyperFlexでは最長で1.2nsと速くなるため、周波数は286MHz(3.5ns)から833MHz(1.2ns)へと上がる。というのは、データをロジックからレジスタへ、レジスタからレジスタ、レジスタからロジックへと転送する場合にはパイプライン的に送り続けることができるからだ。最初の1サイクルは従来と同じようにレイテンシは変わらず遅いものの、ロジックからロジックへ最初に到達した後は格段に速くなる。

図4 HyperFlexアーキテクチャでデータ転送速度を格段にアップ 出典:Altera

最近Intelは、Alteraを買収することを決めたが、IntelにとってはAlteraが2年前に買収したEnpirion(参考資料3)のパワーマネジメントICも魅力。Intelのマイクロプロセッサは、演算処理が遅くてもよい場合は自動的に電源電圧を下げるデジタル電源を使っている。それも10mV程度の細かい単位で電圧を制御する。EnpirionのパワーマネジメントICは、Intelのマイクロプロセッサ用だけではなく、FPGAのように低電圧・大電流のICを動かすために最適なデジタルPOL電源であり、Stratix 10でもEnpirionのチップと組み合わせて使う計画になっている。

最後にセキュリティに関しても触れよう。Stratix 10のセキュリティはSDM(セキュアデバイスマネジャー)で管理する。セキュリティは主に3つの技術で確保する。一つはセクターごとに認証と暗号化を施す。二つ目は異なるタイプの認証を使う。3つ目はPUF(Physically Unclonable Function)機能である。FPGAの各セクターは、コンフィギュレーションとパーシャルリコンフィギュレーションの間に認証し、セクター間のセキュリティを確保する。また、多数の認証キーを個別の構成回路ごとに生成できる。例えば、セクターAの回路ブロックでは、異なる二つのソースを使った認証ができる。PUF機能では、プロセス技術のバラつきから生じる乱数を利用して、FPGAデバイスごとに独自のPUFを持つ。このPUFをFPGAのルートキーを暗号化する。

以上はFPGA部分についてのセキュリティ技術であるが、CPUにはARMを使うため、ARM TrustZoneをセキュリティゾーンとして利用している。Stratix 10 FPGA & SoCのESサンプルは2014年第4四半期を予定している。

参考資料

1. 28nmのFPGAはインタポーザ利用でTbpsを実現、マルチコア内蔵で処理+解析用に (2011/10/26)

2. Intel Custom Foundry EMIB

3. Alteraが高効率電源メーカーのEnpirionを買収した理由とは? (2013/05/17)