Tabula社、FPGA技術で通信用ASSPを製品化、プログラムも可能に

ロジック回路を時分割に駆動して小さなチップで大規模FPGA相当のロジックを実現する米国のベンチャーTabula社がIntelの22nm FINFETプロセスを使い100Gbpsクラスの製品を3品種開発した。100Gbpsのイーサネットブリッジファミリと4チャンネルの100GigEスイッチ、40Gbpsのレギュラーエクスプレッション(正規表現)アクセラレータの三つ。

TabulaのFPGAは、Spacetimeと呼ぶ時分割でロジックを書き換えていく方式のアーキテクチャ。XilinxやAlteraのFPGAだとチップが大きくなってしまうのに対して、小さなチップサイズで同等のロジックサイズを実現するために時分割で、ロジックを書き換えていく。時刻Taまでレイヤー1のロジック、TaからTbまではレイヤー2のロジック、という具合にロジックを時分割で次々と構成・ストア・消去・再構成を繰り返していく。レイヤーを切り替えていく時間は数psと短く、ルータを使い制御する。

図1 Tabula社CMO兼シニアバイスプレジデントのAlain Bismuth氏

この独特なロジックアーキテクチャを開発したTabulaは、このほどFPGA製品というよりもASSPと呼ぶべき高速の通信パケット処理のソリューションにフォーカスしていく。三つの製品群は、このままでも使えるASSPであるが。ユーザーロジックもあり、固定した通信用ASSPは「ロジックの20%程度しか使っていないため、FPGAでカスタマイズももちろんできる」と同社CMOでシニアバイスプレジデントのAlain Bismuth氏(図1)はいう。

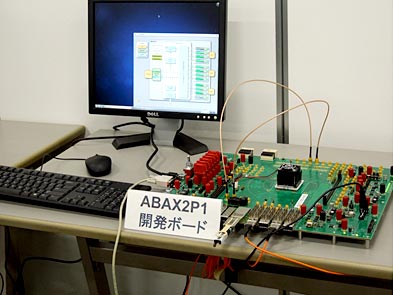

図2 スイッチ開発ボード

これらの製品を紹介する。まず、100Gbpsのイーサネットブリッジは、12チャンネル×10Gビット/秒の信号を100Gbpsのシリアル信号に変換し、その逆も行う。このABAX2P1チップを使い、スイッチ開発ボード(図2)を提供する。このチップは、100Gbpsの次世代ルータやデータセンター向けのスイッチ用を狙っている。100Gbpsと極めて高速にビデオなどの信号を送受信する用途では、光伝送が必須になる。このため、Intelが開発したシリコンフォトニクス技術による光ファイバ送受信モジュール(図3)を利用する。光ファイバは長さ300mまでサポートする。

図3 Intelが開発した送受信光ファイバモジュール シリコンフォトニクス技術を利用

二つ目の製品は、100Gbpsの信号を4チャンネル分スイッチするシングルチップの製品。これもABAXP1ソリューションをプログラムしてASSP的なスイッチ製品に仕上げたもの。これはフレーム単位で通信の意味を持つレイヤー2からLAN同士のスイッチ制御を行うレイヤー3、さらにTCP/UDPヘッダのポート番号を元にパケットの流れを制御するレイヤー4のスイッチに至る一連のスイッチをサポートする。各100Gbpsを送受信するポートを4個持ち、ポート間のレイテンシは500nsと短い。

三つ目の製品40GbpsのRegEx(正規表現)アクセラレータは、ネットワークセキュリティの心臓部という役割を果たす。これはパケット長をチェックして基準パターンとマッチングさせる方法を使って、クロスパケットをチェックする。1Mの基準ルールを持つ。スループットは40Gbps。この製品はパケットやデータのスイッチングを行う最初の二つの製品と組み合わせて、パケットのセキュリティをチェックするもの。

製品は三つともデータセンターや大きなサーバを備えたデータ交換、パケット通信のスイッチやルータなどに使用するハイエンドな商品である。大規模FPGA相当の小面積FPGAの市場として、通信インフラや産業用途を狙っていく。