ザイリンクスがハイエンドのFPGA、Virtex-7HTで28Gbpsの伝送実験に成功

米ザイリンクスは、ハイエンドのFPGAであるVirtex-7 HTを使い、28Gbpsという、超高速のシリアルトランシーバの性能を実証した。1チップでこのような高速のシリアルトランシーバは、これからのインターネットのトラフィック増大に対応した、100〜400Gbpsのバックボーン通信システムを実現するために必要となる。

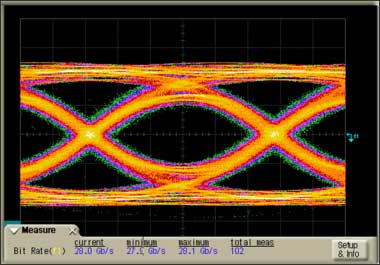

図1 28Gbpsトランシーバのアイパターン

YouTubeの拡がりやインターネットテレビの高解像度化など、ブロードバンドの応用が広がると共にデータセンターやバックボーンの通信システムもパンクしないように帯域幅を広げる必要がある。いたちごっこではあるが、応用の拡大→広帯域化、の進展はまさにとどまるところを知らない。ネットワークシステム企業のシスコシステムズ社の調査では2014年にひと月当たりのトラフィック量が全世界で64EB(エクサバイト:1EBは10の18乗バイト)にも達する見込みだという。通信業者やデータセンター、クラウド業者たちはトラフィック量の増大に対処する方法を研究中だ。2011年過ぎに960Gbpsの通信システム、2014年以降には1.9Tbpsという高速のマルチテラビットシステムが求められている。

高速のデータレートが要求される一方で、装置の大きさは維持することが求められる。すなわち消費電力を下げなければならない。このため装置内の基板ボード1個の大きさは小さくしながら同じ消費電力を保つようにデバイスをより多く使って性能を上げるという手法を用いる。例えば100Gbpsのボードを4枚で400Gbps、全消費電力60Wなら、800Gbpsのシステムを実現するためには、基板のピッチを半減し60Wを維持する。100Gbpsのボードを1枚実現するためには、25Gbpsのデバイスを4チャンネル集積し、それを8枚にして400Gbpsを設計する。全部で32チャンネルとなる。100Gbpsのラインカードを作る例として、28Gbpsで4チャンネルのトランシーバを備え、ASICなどの論理演算処理を含むラインカードにVirtex-7 HTを使う。

図2 CFP(Centi-formfactor pluggable)2と呼ばれるラインカードで実現

ただし、現実の回路として、ロジックデバイスとCFP2オプティックスを結ぶトランシーバではアイパターンが十分に開いているか、がカギになる。このためには位相ノイズであるジッターをできるだけ低く抑えることが求められる。10Gbpsの信号伝送では1ビットの幅は100psなので、最大限許容できるジッターは35psまでだが、28Gbpsとなると約12psまでとなる。今回実証した伝送実験ではランダムジッターが350fs、全ジッターは6psだとしている。しかも今回はテストチップで実験したため、実力値となるともっと下げられる、という。ビットエラー率(BER)の実力は10の-15乗以下だという。得られた性能時での消費電力は明らかにしない。

ジッターを下げるため、ザイリンクスはデジタルPLLを採用せず、ノイズの少ないLCタンク発振のアナログPLLを用いた。加えて、温度変化などに対する信号の変化を調整するための自動キャリブレーション機能回路を設けた。これは受信側でプリント基板の特性をダイナミックにしかもアダプティブに調整する機能だとしている。さらにアナログとデジタルの回路を分離するバリヤを設け、ノイズを5〜15dB減らした。アイパターンを維持するための送信側のプリエンファシス回路、受信側のイコライズ回路を設けていることは言うまでもない。送受信する信号は差動回路で動かしている。

表1 Virtex-7 HTの主な仕様

このFPGAに用いたプロセスは最先端の28nmプロセス。プログラムするためのソフトウエアはすでに入手可能で、デバイスの出荷は2012年前半を予定している。