2Dから3D映像に変換するビデオ処理プロセッサをアイルランド企業が開発

2Dから3D画像に変換するソフトウエアを半導体チップに焼き付けたSoC(ホストCPUと一緒に動作するコプロセッサ)をアイルランドの半導体ファブレスベンチャー、モビダス(Movidius)社が開発した。このチップを組み込みシステムに搭載すると、3次元ディスプレイテレビが簡単にできるようになる。そのための開発ツールも提供する。

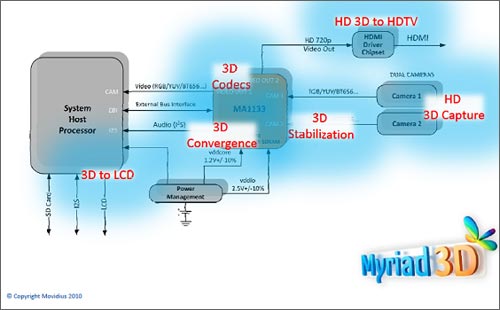

図1 携帯向けの2D→3Dビデオ変換ICをMovidiusが開発

2台のカメラでシーンを撮影してもそのまますぐに3次元の立体画像が見える訳ではない。右と左の目で立体視できるように視差のズレをあらかじめ計算しながら、映像を構成していく。例えば奥行きを強調したい場面は、対象物がスクリーンより前に来るように焦点位置を計算し直す必要がある。立体視の映像は常に計算しながら人間の眼が自然に立体的に見えるように計算を繰り返すことで実現する。

さもなければ、人間が立体的に見えるように見えるように一生懸命に頭脳をフル活用して3次元画像を作りだすことになり、3Dを見ると疲れる、気持ち悪くなる、ということが起きる。それを防ぐためには人間の頭が計算するのではなく、組み込みシステムが計算するように構成しなければならない。それも画面ごとに最適な立体画像が見えるように絶えず計算する必要がある。

こういった計算能力を高めるプロセッサを作ることと、人間が疲れることなく自然に立体視が見えるように最適な計算手法、すなわちアルゴリズムを開発すること、この二つが3D映像装置を作るコツになる。

アイリッシュベンチャーであるモビダスが狙う市場はまずスマートフォンや携帯電話、タブレットPCなどの携帯機器市場。というのは、3次元映像は見る角度の依存性が強いため、携帯機器のように一人で見る応用に向いているからだ。ディスプレイ表面を工夫してオートステレオスコピックなディスプレイで表示すればメガネなしで見ることができる、と同社CEOのショーン・ミッチェル氏は言う。

もちろん、左右の画面を切り替える眼鏡をかけると大型ディスプレイでも3次元映像を見ることはできる。そのためのHD画像もサポートしている。

この半導体チップMA1133は、図2のように、2台のカメラからの映像をRGB/YUVなどの映像信号として入力し、左右の映像の同期をとり合成する。さらにいろいろな3D標準にエンコードし、保存する。このSoCはマルチコアベースのプロセッサであるためプログラム可能であり、新しい規格が登場しても対応できる。

図2 新製品MA1133はホストCPUと一緒に使う

このチップが3次元画像を作り出すアルゴリズムはほぼ次のようになる。ビデオの動きを使い、対象物の奥行きを計算する。その場面の3次元的な奥行きをスクリーンのシーンに合わせて自然に見えるように立体画像を作り出す。

そのためにまずカメラの位置ずれを補正し、次にカメラの傾きや手ぶれ、回転角を補正する。そして2台のカメラの色のずれも修正する。

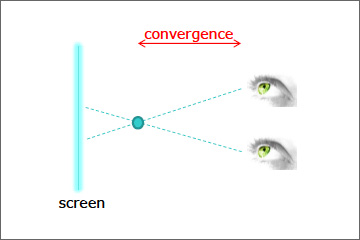

図3 目の焦点がスクリーンより前に自然に来るように計算する

さらに、リアルタイムで特徴をつかみながらビデオ映像の焦点をスクリーンの前方に合わせるという作業を行う。スクリーンの前に自動的に焦点が合うようにリアルタイムで収斂させるが、遠くに物体がある場合にはより立体的に見えるように設計している。この自動焦点収斂によって、カメラとカメラの間隔が広くても立体視が可能になる。視差が70%以上になるように設定したり最大になるように設定したりすることができる。

こういったアルゴリズムを外付けのフラッシュメモリーに保存しておき、システムを立ち上げるとこのアルゴリズムソフトウエアはRAMの方へ転送される。このRAMは8mm角のパッケージの中にSoCとスタックされている。RAMは128MビットのDDRモバイルDRAMチップ。

SoCには自動収斂アルゴリズムやカメラ信号の補正処理、コーデックなどが集積されており、ホストプロセッサとは標準バスでつながっている。消費電力は重い計算処理を行う場合でも数百mWという。プロセッサ部分は8個のShaveCoreと呼ぶベクタープロセッサであり、128ビットの並列処理VLIW命令セットで動く。固定小数点演算器や浮動小数点演算器を内蔵しており、チップ全体のシステムは32ビットRISCプロセッサで制御している。以前発表したビデオエンハンサ・ビデオエディタのチップMA1100と内部構成は同じで、インプリメントするソフトウエアだけが違うとしている。

マルチコアプロセッサのソフトウエアは自社でアセンブラ言語で書く他に、パートナーも使っているが、まだオープンにはしていない。すでに日本のメーカーが採用することは決まっているという。ファウンドリはTSMCで、プロセスは65nmを使う。開発ツールも提供しており、その標準価格は5000ドルである。

図4 開発ボード