新しい市場開拓が可能になったFPGA業界、チャンスと脅威が併存(1)

FPGAビジネスが変貌してきている。米ザイリンクスとアルテラという2強が争ってきた従来の市場でも消費電力を上げずに性能・機能を上げていく方向に変わり、マーケティング努力次第ではローエンド市場にも食い込めることがわかってきた。この2回にわたるFPGAレポートでは、まず従来のハイエンド市場、さらに新規のローエンド市場を見ていく。

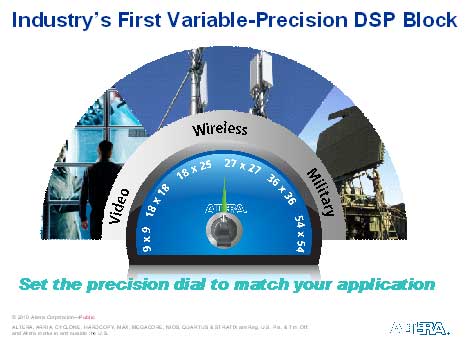

精度を変えられる乗算器を搭載したStratix-5 出典:アルテラ

ハイエンド市場に向け、アルテラは精度を9×9ビットや18×18ビット、18×25ビットなどと変えられる乗算器を多数搭載した新しいFPGA、Stratix-5ファミリーを発表、その応用、狙いについて、米Global Press主催のe-Summit2010で発表した。「固定精度の乗算器だと、高性能なワイヤレスステーションや軍用レーザー、医用画像処理、監視ビデオなどの応用ではコストと消費電力を上げずに性能を上げることはできない」と同社マーケティング担当シニアVPのDanny Biran氏は断言する。

FPGAはハイエンド応用とはいえ、性能を上げれば消費電力やコストを上げてもよいという訳ではない、と同氏はいう。新しい応用に対して、精度の高い計算処理を全ての回路で必要とされる訳ではない。Stratix-5では、18×18ビットの乗算を基本とする乗算器を3,680個も集積しているが、FPGAの乗算器ブロックはソフトウエアで9×9構成や18×25構成に変えることができる。

アルテラのシニアVP Danny Biran氏

これまでビデオ応用では、9×9ビットの乗算で十分だったSD規格のテレビはHDになり12×12ビットへ、4KのフルHDとなると18×18ビットへと進化してきた。ワイヤレスベースステーションでも18×18ビット乗算が必要だった3GやLTEから4GとなるLTE Advancedになると27×27ビットの乗算が要求される。軍用レーダーでもかつては敵機を見つけるだけで18×18ビット乗算だけで済んだが、複数のターゲットを見つけたり、それらを追跡したり、地上のマッピングやシースルー機能を可能にしたりするような機能まで搭載するようになっている。このため数1000台のトランシーバモジュールや数100台のサブチャンネルモジュールを使う。しかも浮動小数点演算という高精度な計算も求められる。

同社はStratix-5シリーズをパワーリミットのMore than Moore製品と位置付けている。3,680個の乗算器に加え、100万以上の論理エレメントを搭載、50Mビット以上のRAMなども集積した。この28nmのFPGAでは、ソフトウエアロジックに加え、同社のFPGAをASICにそのまま落とせるHardCopyブロックを組み込んだ。コスト増加を抑えるためにIC全体のフルマスクセットを使わず、前世代の40nmデザインからメタルレイヤーを少し修正するだけですむようなマスクセットに変えた。2011年の第1四半期にサンプルを出荷する予定である。

設計ツールもビデオ設計のフレームワークや、MatLab/Simulinkモデルを搭載したDSPビルダーツール、マトリックス演算やサインコサイン演算などの浮動小数点演算IPコアなども用意している。ハイエンドのDSPで構成していたレーダーシステムやLTEカード、高速シリアルI/OなどをFPGAで提供することでコスト・消費電力を抑えて性能を上げるシステムを構築できるとしている。

ザイリンクスのFPGAでSoC開発ツールを日立情報が発売

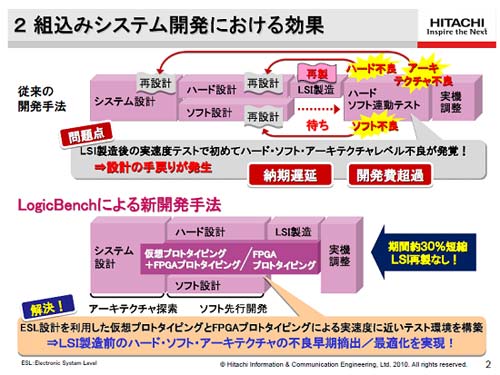

FPGAは、ICを応用機器に直接使うというよりも、システムLSIあるいはSoCを作るためのハードウエア検証に使うためのブレッドボード代わりという使われ方をしてきた。アルテラのライバルであるザイリンクスのVirtex-6を搭載した、システムLSI設計検証用の開発ツールVirtualTurbo-IIIを日立情報通信エンジニアリングが発売した。このツールを使えば、設計したSoCが現実に動くかどうかの設計検証を行うことができる。

日立情報通信が提供するSoC検証システム

システム設計が終わりRTLレベルを出力するとすぐに、ソフトウエア設計とハードウエア設計(ネットリストから物理設計など)に移る訳だが、ハード・ソフトの協調検証やLSIハードウエア回路部分の検証、MatLab/SimuLinkをつかったモデル化やシミュレーションも可能である。SystemCシミュレーションによる仮想プロトタイピングでは、CPUモデルやメモリーモデル、周辺論理モデル、バスモデル、周辺I/Oモデルなどはすでに用意してあり、インターフェースモデルだけをVirtualTurbo-IIIを使いFPGAプロトタイピングで検証すればよい。

このVirtualTurbo-IIIは応用によってゲート数がもっと必要な時は、にVirtex-6 LX760を4個あるいは2個搭載したFPGAモジュールを追加する。4個の場合は高速のスイッチICを使いFPGAを接続している。また、2個FPGAとDDR3メモリーモジュールを2個とFMCコネクタカードを搭載したFPGAモジュールは大容量メモリーや高速インターフェースの検証に使う。