AMDがスパコン・サーバー用ハイエンドのCPUマルチチップモジュールを発売

今やファブレスとして身軽になったAMDが12コア/8コアという極めてハイエンドなマルチコアCPUを発売した。このOpteron 6100シリーズのプロセッサは、HPC(高性能コンピュータ)やスーパーコンピュータなどハイエンドのコンピュータ、サーバー用に使う。Opteronシリーズはすでにクレイのスーパーコンに搭載されているが、このCPUは価格当たりの性能/消費電力を大幅に上げることができる。

Opteron 6100シリーズの外形(左は表面、右は裏面)

Opteron 6100は、45nmのSOIプロセスを使ってグローバルファウンドリーズが製造したものだ。今回はHigh-kゲート材料、メタルゲートはまだ使ってはいないが、32nmプロセスでは使うことになると、同社サーバー/ワークステーション部門ビジネス開発ディレクタのJohn Fruehe氏は言う。

このプロセッサは1辺が数cmのマルチチップモジュール(ソケットG34と呼ばれる1944端子のLGA:land grid array)で構成されており、シリコンは346mm2のCPUチップを2個搭載している。この2チップ構成で合計のCPUコア数が12あるいは8コアとなっている。

このプロセッサ実現のカギは、もはや製造技術でも、コンピュータアーキテクチャでもない。キャッシュ構成やパイプライン段数などはこれまでの最高技術を使っているだけにすぎない。もちろん、1W当たりの性能(性能/W)はこれまでの2.2倍以上と高いのではあるが、セールスポイントは消費電力が低く、性能が高いことではない。むしろ、低コストでこの高性能・低消費電力を実現したことだ。

例えば、2ソケット構成(ICを2個並列構成)の場合に、12コアのCPUではSPECintもSPECfpも同社の従来の6コアCPUと比べても2倍の性能を持つが、整数演算で同じ性能の市販品と比べると、価格は1165ドルと3割も安い。また浮動小数点演算ではこの市販品より価格が3割安いだけではなく性能/Wも20%高い。

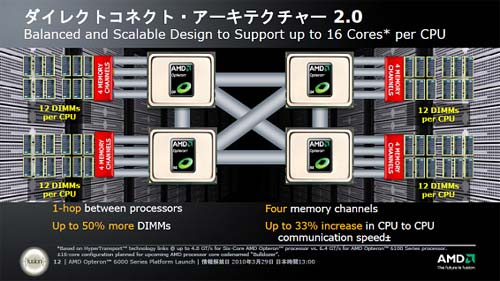

ダイレクトコネクト2.0のアーキテクチャ

これほどの性能/W/コストを実現した技術は、コンピュータアーキテクチャではなく、CPUとCPU、あるいはCPUとメモリーとのやり取りを高速にするための技術ダイレクトコネクト2.0を導入したことだ。この技術はボトルネックとなりがちなインターフェースをスムーズにデータを転送させることでコンピュータの性能を上げるもの。従来のバス方式とは違い、まるで通信交換機のクロスバースイッチのようにCPU同士、メモリーとのやり取りをスムーズにできるようなアーキテクチャである。この構成をとることでCPUとメモリー間の速度は50%向上し、CPU同士の速度は33%上がった。

メモリーチャンネルは4本持ち、それぞれ72ビットバスで低電圧DDR-3をサポートしている。この結果CPU当たりのメモリーバンド幅は最大42.7GB/sになる。CPU同士の接続にはHyperTransportバスを4本用意した。このバス1本には16本のリンクと呼ばれるポートがあり、1リンク当たりのデータデートは最大6.4GT/s(Giga Transfer per second)という。GT/sという単位は、バス幅などによってデータレートが変わるため、インテルなどがこう表現しているようだ。

ダイレクトコネクト2.0アーキテクチャはどうやって実現したか。各CPU内にダイレクトコネクト2.0のポートデータ制御回路を内蔵しており、G34パッケージ内には特別なコントローラを集積していない。このアーキテクチャは高速インターフェースであるHyperTransportをベースにしたスイッチング技術だ、とFruehe氏は言う。理由は将来性を含む拡張性にある。HyperTransportのノード数を上げた超並列(massive parallel)のスーパーコンを低価格で作れるからだ。Fruehe氏は「将来は超並列コンピュータと同様、ノード数を高めていくが、あまり多すぎるとレイテンシが深くなるため、ノード数の数と処理速度のバランスがカギとなる」としている。