米国ベンチャーNetronomeが超ハイエンドなネットワークフロープロセッサを設計

米Intelからスピンアウトし、英Marconiのグループも加わって創立された米Netronome(ネトロノームと発音)社は、IntelからIXP28xxハイエンドプロセッサのライセンスを受け2003年にスタートしたベンチャーである。2回目の資金調達も終わり5200万ドルを得て、このほどネットワークフロープロセッサ新製品NFP-3200のリリースへとこぎつけた。超ハイエンドの応用への売り込みを狙う。

Netronome社CEOのNiel Viljoen氏

創業者でCEOのNiel Viljoen氏は、3Pを備えていることがネットワークプロセッサでは重要だという。3Pとはパフォーマンス(性能)、Power consumption(消費電力)、そしてProgrammability(プログラムできること)。

このネットワークフロープロセッサは、10GビットEthernetからの入力に対して、セキュリティをかけたり解除したりするための暗号化・解読化処理、仮想化コンピュータ処理、DPI(deep packet inspection:パケット構造を解析し何があるのかを調べる)処理といった高度の計算処理を要求するUnified Computing Architecture向けに開発された。しかもネットワークの流れを監視、処理する極めて集積度の高い処理を1チップで実現し、さまざまなネットワークに対応できるようにプログラムできるICである。

既存のプロセッサだと、セキュリティ監視・処理する機能だけを持つプロセッサ、IPやネットワークのプロトコルをプログラムするネットワークプロセッサ、さらに汎用の通信用プロセッサという3つのプロセッサを使ってネットワークの処理を行っていた。今回はこれら3つのプロセッサを統合してシングルチップで処理動作する極めてハイエンドなプロセッサになっている。

上の図にあるように、ギガビットイーサーやセキュリティ機能を高め、マルチコアを持ち、仮想化に対応、DPI機能を持ち、メモリーバンド幅も広いという特長をすべて持つ。

狙う市場は、仮想化技術が強く求められているデータセンターや、ネットワーク機器メーカー、ファイヤウォール企業、ソフトウエアOEM企業、ネットワークインフラストラクチャを扱うハイエンドな企業、など。現在IXPネットワークプロセッサを使っている顧客がアップグレードするという市場も狙える。

主な仕様は以下の通り:

マルチコアアーキテクチャで40個のコアからなり1.4GHzで動作する。命令の処理性能は56BIPS(billion instructions per second)、320同時スレッド発行可能で、30Mpps(packets per second)のスピードにおけるパケット当たりの命令数は1800命令、DPI作業を20Gbpsというスピードで行い、データのフローを制御する。

仮想化技術では、256キューのSRIOV(Single Root I/O Virtualization)規格を持ち、PCIe v2.0のインターフェースを通してx86系プロセッサと通信する。

消費電力性能は、1Wあたり18億3800万命令を処理し、CPUのオーバーヘッドを80%低減できるため性能的には10倍高い。

セキュリティおよび暗号処理技術は標準的な暗号アルゴリズムをカバーし、その速度は20Gbps。

65nmCMOSプロセスで製造。

NFP-3200ネットワークフロープロセッサでネットワークのフローを解析し、x86系チップセットを通してマルチコアCPUで仮想化システムを実現する例が下の図である。

10Gbps Ethernetを通してデータを監視・処理し、仮想化システムを実行する。NFP-3200のSRIOVからPCI Express Gen2の8レーンを経てx86系チップセットに行き、さらにマルチコアCPUへと通信・処理する。Intel系高速シリアルI/OであるQPI(AMD系のHyperTransport相当)をへてマルチコアCPUと直接やり取りする方式は2010年になる予定。

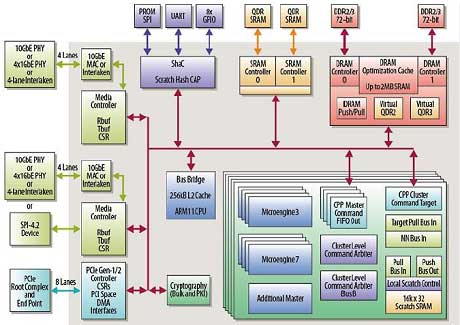

NFP-3200のブロック図は以下のとおりで、Intelからライセンス供与を受けた最初のIXP28xxシリーズから比べて、16コアから40コアのマイクロエンジン(ME)へ拡大、ランバスからDDR2/3へ低コスト化、PCIからPCI Express v2.0へ飛躍的に高速化、XscaleプロセッサからARM11コアへ移行によりL2キャッシュ性能を向上、10Gbps Ethernetを搭載、25GbpsのInterlaken高速シリアルインターフェースを搭載、暗号化アクセラレータを搭載、PKIアクセラレータを搭載、としてIXPプロセッサから機能・性能とも大幅に向上している。

チップのパッケージは40mm×40mmで、ピン数は1521ピン。ハードウエア・ソフトウエアとも開発ツールが揃っている。今後、PCIeに代わりQPIインターフェースを備えたチップも計画している。