材料・デバイス・回路・システムまで網羅するCREST研究成果をCEATECで公開

CEATEC 2019では、大学関係からも実用化に近い研究が発表された。文部科学省傘下のJST(科学技術振興機構)が主催するCREST(戦略的創造研究推進事業)の中で、ナノエレクトロニクスに関する研究3件が、材料からデバイス、回路、システムに至る各レイヤー間の協力を求めるプロジェクト「素材・デバイス・システム融合による革新的ナノエレクトロニクスの創成」の成果を発表した。

図1 CRESTナノエレクトロニクスプロジェクトで今回発表に関わった参加メンバー

左から九州大学浅野種正教授、大阪大学橋本昌宜教授、東京工業大学益一哉教授(現学長)、このプロジェクト研究統括の東京大学桜井貴康名誉教授、東芝セミコンダクター&ストレージ社新領域企画推進部高柳万里子部長、プロジェクト副研究総括の富士通研究所横山直樹フェロー

CRESTのナノエレクトロニクスプロジェクトには、平成25年度から27年度にかけて毎年3〜4件研究が選択され、合計10件の研究プロジェクトが認可されている。今回、その中から、3件の講演と1件のレビュー講演があった(参考資料1)。最初にプロジェクトのアドバイザーである東芝デバイス&ストレージ社新領域企画推進部長の高柳万里子氏から、Society 5.0と、それに必要なエレクトロニクスの役割を紹介し、それを実現するための技術として、サイバーフィジカルシステムのアーキテクチャを紹介した。

この後の3件の講演はいずれも平成26年度のCRESTプロジェクトで認定された研究チームの仕事である。いずれも今年度に終了する。九州大学浅野種正教授をリーダーとする「テラヘルツ波ビデオイメージングの実現に向けて」、大阪大学橋本昌宜教授をリーダーとする「高エネルギー効率コンピューティングを実現するビアスイッチFPGA」、東京工業大学益一哉教授(現学長)をリーダーとする「超高感度慣性センサ・システムが切り拓く世界」の3件をそれぞれのリーダーが紹介した。

テラヘルツで安全なイメージング

浅野教授のチームは、テラヘルツ波を観測するためのイメージングセンサを開発する。テラヘルツ(THz)波は、電磁波と光の中間的な1000GHz以上の周波数の波であり、その波長は0.3mm以下という極めて短い。光の波長では赤外線よりも長い。テラヘルツ波は、柔らかいものを透過するという性質があり、金属はもとよりセラミックナイフを隠し持っていても検出できる。このため、セキュリティチェックや国防利用で注目されている技術である。

THzのエネルギーは4meVと小さいため、X線と異なり人体には安全で、空港での検査を高速にするような応用が期待されている。また、分子間力に依存した吸収スペクトルから、分析にも使われる。THz分光分析(スペクトロスコピー)と呼ばれ、創薬開発へも応用できるという。しかし、単にセンサ1素子では機械的に走査しなければならず、画像として撮影するには数時間もかかってしまう。

そこで、浅野教授チームが進めるのは、テラヘルツセンサ素子をマトリクス状に並べて、まるでカメラのように画像を撮影するイメージングデバイスである。機械的な走査よりも高速に画像を得ることができる。THzの長さはもはやミクロン単位であるため、チップ上にアンテナを加工でき、検波器となるInGaAsのHEMTトランジスタ上に形成する。移動度が高く電気抵抗が小さいためTHz波を検出する。ただし、検出電圧は13〜14µV程度と小さいため、この後に周波数変換や増幅が必要になる。最終的にデジタルに変換しSPIインターフェイスによってCPUに送ることができる。

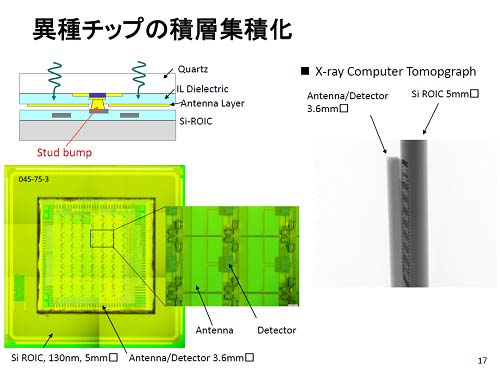

図2 異種チップ同士を積層接合するTHzイメージセンサ 出典:九州大学浅野種正教授

開発した2次元THzイメージセンサ(図2)は、ノイズレベルが1.8pW/√Hzと小さく、1THzの信号を受信できたという。プロセス的には薄い化合物半導体膜とアンテナ素子との接合や、Si基板上への貼り付けなど、手間のかかる工程が必要となる。市場もデバイスも量産すべき製品にはなりにくいが、セキュリティ上では欠かせない半導体チップになりそうだ。

小さな面積でAI向きのFPGAを目指す

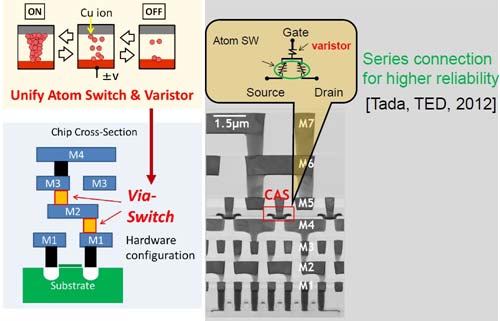

2番目の講演の橋本教授チームの研究は、プログラミング素子とCMOS回路を重ねることでチップ面積を削減し、性能・消費電力を改良しようとするFPGAである。プログラマブルなロジックとして、ソフトウエアで処理するCPUやGPUと比べると、ハードウエア回路をプログラムによってカスタマイズできるFPGAは、規格変更や仕様変更が激しい通信用途や周辺機器で使われることが多いが、SRAMスイッチを使っているため面積が大きく価格が高くなってしまう。

橋本教授のチームが考えるFPGAは、プログラム素子として従来のSRAMに代わり、固体電解質の中でCuイオンの移動によって、導通・非導通状態を作り出すビアスイッチを利用する(図3)。マトリクス状に原子スイッチを構成し、さらにプログラムする時の選択ダイオードとしてバリスタを設けている。LUT(Look Up Table)のロジックとして利用するCMOS回路はシリコン基板内に形成し、プログラム用のビアスイッチは、多層配線層の中に形成する。このため、FPGA全体の面積は減る。

図3 Cuイオンの移動によってオン・オフを実現するビアスイッチと選択バリスタ 出典:CREST、大阪大学

この新しいFPGAでは、CMOS回路部分にはLUTとSRAM、MAC(積和演算器)を規則的に配置しており、AIの推論演算をできるようなアーキテクチャをとった。スイッチ部分はクロスバー構造を取り、プログラミングによってドライブしないスイッチには影響を及ぼさないことを確認している。今後はFPGAの試作と評価を進めていく。

高感度センサでパーキンソン病を早期発見する

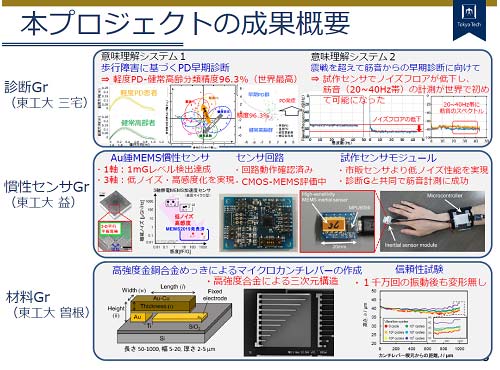

益一哉教授のチームは、超高感度の加速度センサを作り、パーキンソン病の早期発見・早期治療を目指す。2013年以前のプロジェクトの時は分解能1mGレベルの感度(分解能)だったが、現在は4ケタ低い、0.1µGまでやってきた。

加速度センサは、シリコンMEMSにAuの重りを先端に載せることで感度を上げてきた。このためAu系(正確には合金)材料の開発、加速度センサデバイスの開発、そして測定結果からデータを機械学習で分析し健常者とパーキンソン病患者とを診断する(図4)。

図4 高感度加速度センサでパーキンソン病を早期発見するシステム 出典:CREST、東京工業大学

材料グループはMEMSカンチレバーの先端に取り付けたAu合金の加速度センサの物性特性を調べ、Au合金は固く合成に優れているという常識外れの結果を得ている。デバイスグループは、加速度センサからの信号を増幅し、信号を読み出す回路やそれを表示する回路などをプリント回路基板上に実装し、腕に装着できるところまで作っている。しかも高感度なカンチレバーのセンサができたおかげで、感度が上がりこれまでのセンサと比べてノイズフロアが大きく下がった。

診断グループは、歩行障害を検出するために健常者と患者、健康な高齢者などの歩行時の足の高さと歩幅のデータを収集する。さらに、震えの方向を1軸だけではなく3軸に広げたセンサも作った。これらのデータを機械学習によって、軽度のパーキンソン病患者、若い健常者、高齢の健常者などを区別できる範囲を求めた。診断グループは病院とも協力しており、材料からプロセス、デバイス、回路、システム、応用までレイヤー間のコラボレーションを実現した。

これら3件のCRESTの研究事例は、全て実用化を念頭に置いた「開発」である。ただ単に研究するだけではない。このため、材料、プロセス、回路、システムのレイヤーごとに協力することが求められている。このようなレイヤー間の産学プロジェクトは今回のCRESTナノエレクトロニクスプロジェクトが初めてである。

参考資料

1. 超省エネルギーIoT社会実現に向けたナノエレクトロニクス技術 〜イメージング・センサ・コンピューティングから拓くイノベーション〜 (2019/10/16)