Intel、技術ロードマップを発表、2025年にTSMCを追い抜く

Intelがこれからのプロセスとパッケージング技術の2025年までのロードマップを発表した。プロセス製造技術とパッケージング技術の両方を活かし、Intel 7からIntel 4、Intel 3、Intel 20A、さらにIntel 18Aと呼ぶプロセスノードを設定し2025年以降も展望した。CEOのPat Gelsinger氏(図1)は盛んに「Intel is back」という言葉を連発した。

図1 Intel CEOのPat Gelsinger氏 出典:Intel Corp.

2月にGelsinger氏が就任してIntelに戻ってくるまで、財務出身の前CEOは研究開発投資に二の足を踏んでいたため、エンジニアたちのモチベーションは下がり、退社したエンジニアも多数いた。前任のCEOはワンポイントリリーフと見られていた。前任者の前のCEOが不倫騒動で辞めたことでCEOになっただけだったからだ。産業界からも、技術のわかる新しいCEOを求める声が上がっていた。

Gelsinger氏は就任早々、IDM 2.0方針を打ち出し、テクノロジー企業のIntelはもっと製造プロセス技術に力を入れることを訴求した(参考資料1)。今回の発表は、IDM 2.0の状況と新ロードマップの発表で具体的にこれからのテクノロジーの方向を示す場となった。

IntelのSuper FinFETの10nmプロセス(参考資料2)は、メタルピッチはTSMCの7nmプロセスと同等であったが、Intelの方が遅れている、というイメージを埋め込まれてきた。現在、10nmプロセスは、アリゾナ工場、オレゴン工場、イスラエル工場で量産しており、「うまくいっている」とGelsinger氏は述べている。このプロセスと比べると7nmノードに相当するIntel 7プロセスは、性能が10〜15%上がっているという。

Intel 7プロセスはトランジスタレベルの最適化を図り、歪や材料の改良などで電子の走行速度を上げたと、同社技術開発部門のシニアVP兼ジェネラルマネージャーのAnn Kelleher氏は述べている。エネルギー制御を改善しパワーデリバリ技術も改良したことで、今年後半にはクライエントPC向けのAlder Lake製品が出てくるという。またデータセンター用のSapphire Rapidsは2022年第1四半期にリリースされる予定だという。

さらに4nmノードに相当するIntel 4プロセスを使うクライエント向けMeteor Lake(メティアレイクと発音)製品は、2021年第2四半期に、テープインに入りコンピュータタイル(チップレット)を製造する。データセンター向けにはGranite Rapids製品を用意している。

Intel 4ではEUVを使っていく。IntelはASMLとは長い間、共同で開発してきたという歴史があるとして、EUVマスク製造のドイツIMS nanofabrication社とも一緒にやってきた。これからのEUVパートナーとして、Applied Materials、東京エレクトロン、Lam Researchの名前も上げた。EUVの先は高NA技術を使うEUVになると見る。

Intel 3は2023年第2四半期での実現を目指し、トランジスタの性能/Wは18%向上するという。高性能ライブラリやドライブ電流の増加、配線メタルスタックの最適化、EUVリソグラフィの利用増強などの技術を使う。

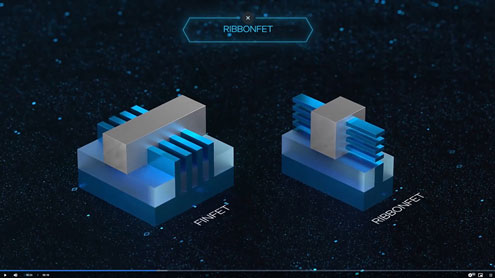

図2 ゲートオールアラウンド構造のRibbon FET技術 出典:Intel Corp.

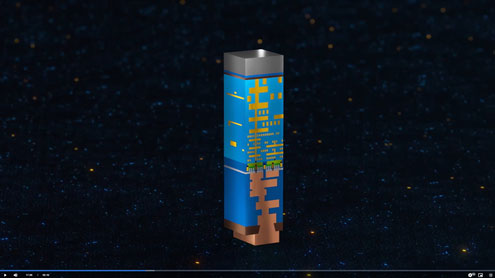

TSMCに追いつくのはIntel 20Aからだ。ここでの20Aは20Å(オングストローム)ノードを示唆するネーミングとなっている。このノードでは、ゲートオールアラウンド構造のRibbon FETトランジスタアーキテクチャ(図2)と、PowerViaと呼ぶ新しい背面電源ラインを使うパワーデリバリーネットワーク(図3)を使う。これらの新技術は、90nmでの歪シリコン、45nmでのハイKメタルゲート、22nmでのFinFET、10nmでのSuperFinFET技術に続く、新テクノロジーとなるという。

図3 電源ラインをトランジスタの下側に構成するPowerVia技術 信号ラインはトランジスタより上の多層配線層に形成する 出典:Intel Corp.

PowerVia技術はトランジスタの下側のバルク側に電源ラインネットワークを構成し、信号ラインは、トランジスタの上側に多層配線として構成する技術である。2024年にはIntel 20Aノードを備え、2025年初めにはIntel 18Aを開発するという計画だ。

Intelは、パッケージング技術においてもこれまでは平面上のチップ同士を小さな再配線チップで接続するEMIB(イーミブと発音)技術や、チップをTSV(Through Silicon Via)でスタックする3D-IC のFoveros(ファベロスと発音)技術を示してきた。特にFoveros技術をEMIBと組み合わせて横方向に展開するFoveros Omni、さらにはハンダボールではなく銅ピラー同士でチップ間を接続していく3D-ICのFoveros Direct技術などへと発展させる計画だ。Sapphire Rapids製品ではレチクルサイズの2倍のチップとなるが、EMIBの活用で標準パッケージ製品と比べ、バンド幅が2倍、電力効率は4倍となる計画だ。

狙いはこれまでのTSVによるチップペネルティを最小限にするとともに、電源ラインもさまざまな選択肢を用意することだ。またFoveros Directでは銅ピラーのI/Oピッチを25µmと微細化し、バンプ密度を10k接続/mm2へと上げバンド幅の広い配線を製造できるようにする。これらは2023年までにメドをつけ、ヘテロプロセッサの集積や機能ブロックレベルのパーティショニングを可能にしていく。Letiやimec、IBMとパッケージでも共同開発を行っており、将来への展開に自信を持っている。

IntelのIDM 2.0は自らもファウンドリサービスを提供するとしているが、Lab to Fabのパイプライン、すなわちファウンドリサービスIFS(Intel Foundry Service)を米国と欧州に展開する。潜在顧客は100社を超えているが、今回は2社を紹介した。

IFSで最初の顧客はAWS(アマゾンウェブサービス)だという。ここではデータセンターのインフラ向けのパッケージソリューションで提供するという。AWSはすでに自前のチップGraviton IIを使っており、Intelとのコラボチップはその次の製品ではないかとみられる。

また、名前を出しても良い顧客としてQualcommも上げた。QualcommのCEOであるCristiano Aman氏が「Intel 20AのRibbonFETとPowerVia技術にワクワクしている」と述べたコメントを披露した。Amon氏は米国において先端ファウンドリを使えることを喜んでいるとした。Qualcommは、モバイルコンピューティングのプラットフォームをIntelと共同で生産することになりそうだ。

Gelsinger氏は、今のところ2社の名前しか出せないが、産業用と自動車用の半導体で話し合い中だと述べている。2024年にはTSMCに追いつき、2025年にはファウンドリのリーダーにもなると意欲的だ。オンライン会見では、パッケージングやプロセスの責任者も登場しており、いずれも自信に満ちた発言を行っている。

参考資料

1.「Intelの200億ドル投資は、製造力強化の序の口」、セミコンポータル (2021/03/25)

2. 「Intelの11世代プロセッサ、微細化よりもFinFETと多層配線に工夫」、セミコンポータル (2020/09/04)