「ダブルパターニングが曲者」を露呈したFinFET技術のSPIフォーラム

セミコンポータル主催のSPIフォーラム「3次元プロセスの壁とソリューション」が1月30日、東京御茶ノ水で開催された。ここでは、16/14nm時代から本格的に導入されるFinFETや、NANDフラッシュのような縦型メモリといったプロセスの3次元化を採り上げた。2014年12月のIEDMでもFinFETが大きなトピックスを占めたようだ。

図1 FinFETの最新動向を述べる東京大学 平本俊郎教授

最初の講演では、東京大学生産技術研究所の平本俊郎教授(図1)がFinFETの最新動向とIEDMにおけるFinFET技術について述べた。TSMCの16nmバルク、Intelの16nmバルク、IBMの14nmSOIのそれぞれを紹介した。TSMCはトランジスタ断面写真を見せていない上に、性能が向上したことを述べたという。IntelのFinFETはこれまで微細化でVthのバラつきが大きくなる方向だったが、FinFETにすると、22nmでバラつきが減少し、14nmはさらに減少し。90nmプレーナバルクに近づいている(図2)。もちろん、ゲート直下はノンドープによって不純物の影響によるばらつきを抑えた構造である。IBMはSOIのFinFETを使い、しかもVthの調整用に仕事関数の異なる2種類のメタルを使った例を示した。SOIのFinFETはFinがバルクよりも低いため、ウェーハコストは高くても、トランジスタ形成コストはむしろ下がると見ている。

図2 Intelの16nmバルクFinFET技術はバラつきが減少している 出典:IEDM 2014 講演番号3.7

ファウンドリのUMCはもちろん、16nmFinFETの開発を進めているが、同社のFinFET技術はIBMと共同開発してきたもの。同社Corporate DevelopmentのVPであるJ.J. Wu氏は、高性能な16nm FinFETだけではなく、低コストFinFETも開発しており、それらを使い分けると述べた(表1)。低コストFinFETはコストの高いダブルパターニングを使わない方式のFinFETであり、デザインノードでは28nmに相当するとしている。

表1 UMCの提案する低コストFinFETと16nm FinFETのミックス

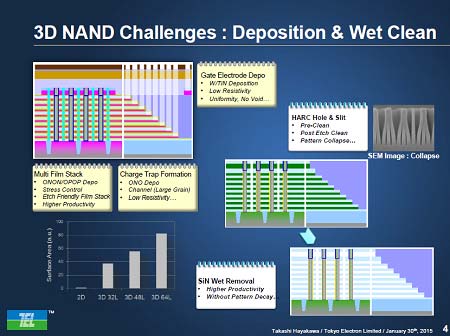

UMCのプレゼンでも述べていたように、アスペクト比の高いFinFET技術の歩留まりの決め手はどうやら、ダブルパターニングのようだ。それを裏付けるかのように、東京エレクトロンのSPEマーケティング・プロセス開発本部の早川崇氏は、Fin FET技術に限らず、28nm、20nm、14nmと微細化されても集積回路内のトランジスタ単体のコストは下がらなくなっていると述べた。その理由は、ダブルパターニングによって歩留まりが下がるからである。28nmがダブルパターンを使わなくて済む最後のリソグラフィノードとなる。14nm時代ではFinのパターン崩れの問題も付きまとう。

DRAMやNANDフラッシュのようなメモリもアスペクト比が50〜80と極めてシャープな形状のピラー構造が必要になる。3次元NANDフラッシュでは、バルク内に形成された数十の層とコンタクトをとるために、少し削っては場所を少しずらす、という作業を繰り返すことになる(図3)。工程が増える分だけ3D-NANDフラッシュ構造は40%程度コストアップになるという。コストに見合うようにするために3ビット/セル構造が主流になるようだ。総じて、いかに安く作るかが最大の課題となる。

図3 3次元NANDフラッシュのコンタクト形成は工程数が多い 出典:東京エレクトロン

ルネサスエレクトロニクスはIEDM 2014で16nmFinFET技術によるSRAM試作を発表した。SRAMは単なるメモリやキャッシュだけではなく、プロセッサのレジスタやバッファメモリによく使うため、SRAMを評価TEGとして試作する意味は大きい。同社は、カーエレクトロニクス分野で2020年を目指した「統合コックピット」というコンセプトを発表している。今回の16nmFinFETプロセスによる256KビットSRAMはファウンドリのTSMCが製造したものだが、このSRAMを集積したシステムLSIは2020年に照準を合わせたもの。45nmの第1世代、28nmの第2世代、そして16nmFinFETプロセスの第3世代のシステムLSIとして性能を上げていく。自動車の統合コックピットでは、画像認識や画像処理などをリアルタイムで行う必要があるため、性能向上への要求は強い。このためメモリ容量の増大と、処理速度の向上がCPUを速くする。

今回6トランジスタ構成のFin FET SRAMセルでは、負荷トランジスタ、駆動トランジスタ、パストランジスタ同士の電流比は1対1になってしまう。1対1だと書込みにくくなるため、Finの数を増やすことで電流比を大きくした(図4)。加えて、書き込み時にはバイアスを上げてパルス幅を広げるためのアシスト回路を設けた。この結果、マージンが高くなり、高速化できるようになったとしている。

図4 FinFETだとSRAMセルのトランジスタの電流比により書込みが困難になる 出典:ルネサスエレクトロニクス

FinFET技術はトランジスタ同士の距離が近いローカルでは、バラつきが減るが、1チップ上で離れたトランジスタ同士は大きくバラつくとしている。

FinFETのような3次元プロセスは、製造だけではなく設計上も課題が多い。EDAツールも改良を迫られている。特にダブルパターニングやFinFETの形状やそれに基づく抵抗と容量の抽出が難しい。このため、ダブルパターニングとFinFET向けのツールが欠かせない。Mentor Graphicsは、自社の物理検証ツールCalibreを改良して、FinFETに向けたパターンの幅や間隔のルールチェックを可能にするモデルを開発している。

FinFET技術は、設計から製造プロセス、製造装置など幅広い分野に及ぶテクノロジーである。このセミナーは、このことを再認識させる構成を採った。