TSMCが台湾で次々と建設する "Advanced" Backend Fabとは何?

前回のブログ(参考資料1)で、TSMCの台湾域内だけではなくグローバルなファブ一覧を示したが、実はこれがTSMCのファブのすべてではない。前回紹介したのは、前工程(Frontend、ウェーハプロセス工程)のファブだけであって、実は「先進的な後工程」(先進アッセンブリと最終テスト)のファブが以下のように台湾内の5ヵ所に点在している。これらの既存ファブとは別に今後さらに2つのファブを増設する見込みである。

既存工場

Advanced Backend Fab 1 台湾・新竹

Advanced Backend Fab 2 台湾・台南

Advanced Backend Fab 3 台湾・桃園 (新竹市の北方)

Advanced Backend Fab 5 台湾・台中

Advanced Backend Fab 6 台湾・竹南 (苗栗県)最先端全自動製造ライン

計画中の工場

(Advanced Backend Fab 7) 台湾・銅鑼(どうら)(苗栗県) 2024年着工

(Advanced Backend Fab 8) 台湾・嘉義県か曇林県 検討中

図1 2023年稼働の最新のTSMC Advanced Backend Fab 6 出典:TSMC

Fab 4 が欠番になっているのは、前回説明したように、日本語同様に中国語でも4は忌み数だからである。

TSMCは、単にBackend Fab (後工程工場)と言わずに、わざわざ「Advanced (先進的)」をつけているのだろうか?台湾には多数の後工程受託専門業者Outsourced Semiconductor Assembly and Test(OSAT)が存在し、前工程担当のファウンドリと分業してきた。しかし、3D-ICの登場で後述するように前工程と後工程の境界があいまいとなった上に、独自開発の3D-ICアセンブリ技術の秘密保持のために、先端デバイスに関しては、ファウンドリが後工程も内製化するようになってきている。

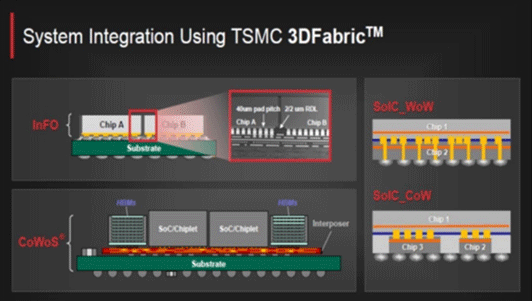

Advanced Backend Fabのうち、最も新しい施設は竹南サイエンスパークに2023年6月に開所したばかりのAdvanced Package Fab 6(図1)で、同社の3D(3次元)実装技術「3DFabric」(図2)(参考資料2)に対応する初の全自動化パッケージング/テスト工場となっている。つくばのTSMC 3D R&D Centerのクリーンルーム(図2)は、台南のAdvanced Backend Fab 6とコピーイグザクトリのレイアウトになっており、つくばでの研究成果をそのまま台湾の工場に移管できるようになっていると言われている。

図2 TSMCの3D実装の総称である3D Fabric 出典:TSMC

先進後工程のクリーンルーム内部は一切公開されていないが、つくばのTSMC 3D-IC R&D Centerの竣工直後の装置搬入前の写真が1枚だけメディアに公開されているのでご覧になられた方も多いだろう(図3参照)。前工程同様のウェーハ収納ボックス自動搬送システムが天井張り巡らされている。前述したように、台湾の最先端のAdvanced Backend Fabとコピーイグザクトリのレイアウトと装置構成になっているため、部外者の立ち入りや写真撮影は許可されていない。

図3 つくばのTSMC 3D-IC R&D Center クリーンルーム内部 出典:TSMC

集積回路が2.5D、更には3D化するにつれて後工程も高度化してきて、クリーンルームの清浄度も製造装置も前工程並みとなり、製造に使用される製造装置も前工程用が一部転用されるようになってきたため、更には複数のチップを接続する高度なプロセス技術の秘密保持のために、ファウンドリも先端製品に関しては独自の後工程工場(Advanced Backend Fab)を建設するようになった。TSMCは、AIチップ向けCoWoS(注)プロセスの生産能力が急激な需要増加に対応できていないため、一部を外部委託するとともに、Advanced Backend Fab 7を台湾苗栗県に2024年末までに起工することにしているほか、Advanced Backend Fab 8を台湾嘉義県か曇林県に建設することを検討している。

(注)CoWoS:Chip on Wafer on Substrateの略。2012年にTSMC社によって開発された高性能チップ向け高密度パッケージング技術。NvidiaのAI チップセットの実装に多用されており、TSMCでは生産が追いつかず、一部OSATに製造委託している。構造例を図2左下に示す。

前工程と後工程を取り持つ「中工程」とは?

従来半導体製品の後工程は、台湾に多数存在するOSATが分担してきたが、AIチップはじめ先端半導体製品の後工程は複雑で、秘密保持上、ファウンドリ社内で行うケースが増えている。

チップレットの登場で、前工程と後工程の境界があいまいになり、チップレット間をシリコンインターポーザーやブリッジチップを用いて接続するには前工程の技術が必要だし、電源供給を裏面から行う、いわゆる 裏面電源供給ネットワーク(BSPDN)を形成するためのウェーハ極薄化には後工程の技術が必要となる。前工程と従来の後工程の中間に位置し、前工程と後工程の技術が混在する工程を、最近「中工程」と一部で呼ばれるようになった。今後、3D-IC実現の要となる中工程が更に注目されるようになるだろう。

ただし、「中工程」の定義はあいまいである。ディスコは、同社が担当するグラインディング(研削によるウェーハの薄化)からダイシング(切削によるウェーハの個片化)までの工程を「中工程」と呼び、アッセンブリ以降の後工程と区別しているが、これは同社独自の定義である。

訂正と情報更新

WaferTechはTSMC Washingtonに社名変更

前回掲載したTSMC場部一覧でFab 10とFab 11が入れ違っていたので、以下のように訂正させていただく。

Fab 10 中国・上海

Fab 11 米国ワシントン州

なお、Fab 11は、WaferTechという社名だったが、2023年12月15日、TSMC Washingtonと社名変更した。同社は、1996年にTSMCとAnalog Devices(ADI)、Integrated Silicon Solution Inc(ISSI)、およびAltera(現Intel)の合弁会社として、米国初の200mm専業ファウンドリとして誕生した。2010年にTSMCの100%子会社となったが、社名は変更されずにいた。今回の社名変更は、このファブがTSMCの傘下にあることを周知し、アリゾナに新工場建設中のTSMCの米国における存在感をさらにアピールする狙いがあると言われている(参考資料3)。

参考資料

1. 服部毅、「台湾TSMC社のファブ23はどこにある?ファブ23フェーズ1とは何?」、 セミコンポータル (2023/12/12)

2. 服部毅、「TSMCの会長が語った3D IC技術の現状と将来展望 - ISSCC 2021」、マイナビニュースTECH+ (2021/02/25)

3. 服部毅、「TSMC、米国子会社のWaferTechの社名をTSMC Washingtonに変更」、マイナビニュースTECH+ (2023/12/21)