高濃度Si基板を貫通電極基板としてMEMSに応用

スウェーデンに本社を置くSilex Microsystems社は、高濃度シリコンウェーハを使い、円柱のSi貫通電極を残す方式のTSV(through silicon via)技術を開発、MEMSパッケージングへの応用を示した。

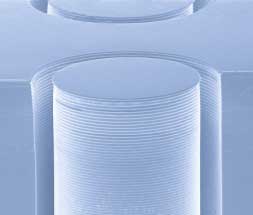

これは、抵抗率の低い(高濃度)シリコンウェーハに直径35μm〜200μmのビアを残して、その周りを幅15μm〜20μmに渡って溝を掘り、その溝をウェーハを貫通するまで、くりぬくというわけだ。できた溝を絶縁膜で埋め尽くす。このようにして真ん中の高濃度シリコンが貫通電極となる。

Silexはこの技術をSemiconductor International日本版主催のMEMSセミナーで発表した。貫通電極をチップのボンディングパッド部分に形成したり、貫通電極だけのチップとCMOS回路だけのチップとを張り合わせたり、あるいは貫通電極とMEMS部分を張り合わせたりするなど、さまざまな応用の可能性を示した。シリコン同士の張り合わせは熱膨張係数が同じであるため信頼性が高い。

Silex社は、現在6インチ・ウェーハを使用するMEMS専門のファウンドリ。2000年に設立され、すでに60社の顧客と100種類以上のMEMS製品を製造した実績を持つ。同社セールスディレクタのMagnus Rimskog氏によると、2008年には8インチラインを作るという。今回のTSV電極を構成するチップあるいはウェーハをスターティング材料として供給する。

貫通電極は、まずドライエッチングで周辺に溝を掘ることから始まる。ボッシュプロセスと呼ばれるエッチングとデポジションを繰り返しながら、均一な幅の溝を掘っていく。装置はアルカテル製だという。溝を掘るのにかかる時間は数十分ですみ1時間未満で終わるという。最初の装置開発時は3時間もかかったとしている。そのあと、絶縁膜を高温で形成し、溝を絶縁材料で埋めていく。最後にCMPで裏面を削り貫通電極を露出させる。

溝を掘れる可能なウェーハ厚さは600μmまで、ビアのピッチは50μm以下、アイソレーションの溝の幅は10〜15μmだという。ビア平面の形は丸でも四角でも長方形でも可能。電気抵抗は、例えば100μmの直径でウェーハの厚さが400μmの場合、1Ω程度だという。

Rimskog氏によると、エピタキシャルウェーハにして、貫通電極を形成するつもりはない。貫通電極は貫通電極としてのウェーハを作るとしている。ウェーハレベル・パッケージング技術を使い、センサーや貫通電極、CMOS回路などそれぞれのウェーハで作り、シリコン同士をアセンブリする。