NANDフラッシュを16個管理する携帯機器向け周辺チップをCypressが開発

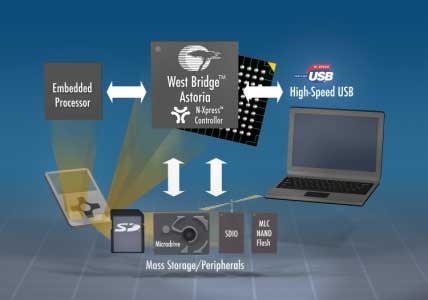

組み込みシステムの周辺チップであるウェストブリッジと呼ぶ周辺LSI「Antioch」を米Cypress Semiconductor社が昨年発売したが、このほど携帯機器への組み込みシステムを意識し、多ビット/セルのNANDフラッシュを16チップサポートし、SD/MMICカードのサポートやSDインタフェースなどを強化した周辺チップ「Astoria」を開発、サンプル出荷した。

組み込みシステムでのウェストブリッジと呼ぶ周辺チップは、パソコンシステムでCPUとメモリーをつなぐノースブリッジ、さらにそのノースブリッジと周辺機器とをつなぐサウスブリッジを真似て、組み込みシステムのCPUと周辺機器を結ぶ回路をウェストブリッジと呼んでいる。パソコン以外にプロセッサとメモリー、周辺システムからなる組み込みシステムでは、従来のCPUは周辺機器とつなげるためのインタフェースをすべてサポートしていなかった。

このようなウェストブリッジチップがあれば、CPUと周辺とのやり取りがスムーズになる上、さらに高速の周辺インタフェースが登場する時にも対応できる。時にはCPUに負担をかけることなく周辺からメモリーへ、あるいは周辺から周辺へと直接やり取りでき、CPUへの負担を軽くすることができる。ちなみにこのチップを使った携帯組み込みシステムで1Gバイトのデータをダウンロードする時間は、そのチップを使わない携帯電話や、スマートフォンと比べて1/6〜1/32の時間で済むという実験を行っている。

昨年開発したウェストブリッジチップAntiochは、USBおよびマスストレージコントローラとCPUとをつないだが、フラッシュとの接続は2バンクしかサポートしていなかった。

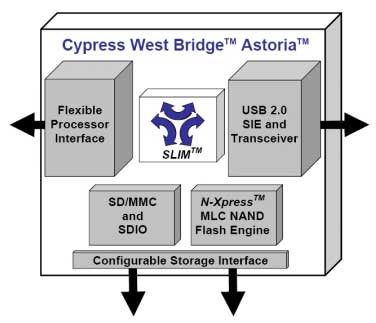

今回開発した第2世代のウェストブリッジチップAstoriaは、最大16個の多値(4ビットまで)NANDフラッシュチップや、SDインタフェースなどをサポートしている。多値NANDにこだわるのは、ギガバイト当たりの価格が1ビット/セルのNANDフラッシュよりも安いからである。しかし多値NANDフラッシュは1ビット/セルと比べて書き込み時間が長いなどの問題があり、誤り訂正やブロック管理、不良ビットの平準化などが難しかった。

Astoriaはこのような問題を解決し、N-Xpressと呼ぶフラッシュコントローラ回路を開発した。このコントローラ回路には、最大4ビットまで誤り訂正できるReed-Solomon符号によるECC(誤り検出訂正)回路、不良ブロックの管理回路、不良ビットの平準化回路を内蔵した。さらにダイナミックなインタリーブ回路をNANDフラッシュとのインタフェースに設け、16個のNANDフラッシュを管理できるようにした。インタリーブ回路は8ビットバスが2本あり、それぞれ8個ずつのNANDフラッシュをつなぐことができる。

さらにSD/MMICカードなどのストレージデバイスとのインタフェースやSDIOインタフェース回路のエンジンも設けた。もちろん、従来のAntiochと同様、組み込みプロセッサとのインタフェース回路や、パソコンなどとのUSB2.0インタフェースも設けている。

誤り訂正回路では、4ビット/セルの場合でさえ、セル内だけではなくセル間のビット誤りに対しても検出訂正できる。メモリーセルには関係ない。セルの配置は、1ブロック当たり512バイトからなる。ただし、多値セルのNANDフラッシュでは3ビット/セルまでが現実的に設計できる多値だとフラッシュメーカーは見ている。

これだけの回路を内蔵しておきながら、消費電力は以前のAntiochと同じ程度で、スタンバイ時に50μA、動作時は数100mAだという。電源電圧は1.8V〜3.3V。パッケージは6mm×6mmで、ボールピッチ0.5mmのBGA。来年前半には量産に入る。価格は前回のチップ並みだとしている。