Mentorがファーストシリコンの一発完動を実現する強力ツールを発表

米Mentor Graphics社は、45nmプロセス以降のLSIを歩留り良く作るための物理設計・検証・歩留まり向上までを含めた物理設計ツールをDAC (Design Automation Conference) 2008でリリースした。半導体プロセスのリソグラフィ寸法が光の波長(かつてはリソグラフィの限界寸法と言われた)よりも短くなってきているため、パターン通りの寸法を加工することが難しくなってきている。それを試行錯誤で補正してきたが、今回のツールはタイミングからプロセスのバラツキまで含めて自動化しようというもの。

LSIの設計分野は、システムに近いレベルではなじみの薄いVHDLやVerilogに代わって、もっと楽に誰でも設計できる方法として、C言語設計をベースにするESL(electronic system level)が注目されている。Cによるプログラミング言語で設計したあと、コンパイラでRTLレベルまで変換するわけだが、RTLレベルの技術はもはや完成し尽くしてほとんど話題にも上らないが、RTLレベルから物理的な配置・配線を描くところがいま大問題になっている。

論理レベルでは実際のタイミングを検証できないため、欲しい性能が本当に得られるとは限らない。チップをシリコンに焼き付けてから性能が出ない、というようなことはもはや許されない。それも「ゲート遅延や配線遅延のモデルはもはや過去のものになり、今やノイズやシグナルインテグリティがチップレベルで求められるようになってきている」、とMentor社Design-to-Silicon部門の副社長兼ジェネラルマネジャーであるJoe Sawicki氏は述べる。タイミングの遅延やクロックスキューを防ぐだけではない時代に突入した。

タイミングだけではない。リソグラフィでパターン通りの寸法をそのまま加工できないという時代にも入っている。物理設計とマスクデータとの間の関係がこれまでになく、緊密な関係が求められる。

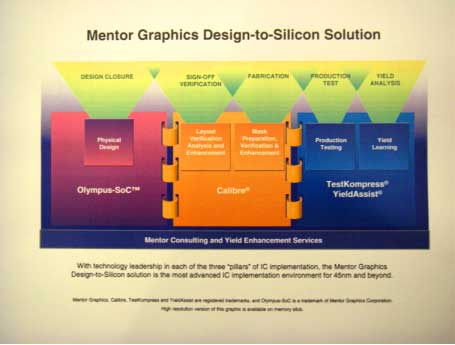

今回Mentorが新時代の物理設計ツールとして示したのは、三つの大きな柱からなるツールである。LSI上のさまざまな回路の配置とそれらやその内部をつなぐ配線の設計システムOlympus-SoCと、チップの配置配線が正しい結果を検証し、さらにリソグラフィの補正まで行うCalibre、そして三つ目はLSIの論理動作をテストし歩留り解析を行うTestKompress/YieldAssistである。これら3本のツールを統合してファーストシリコンの一発完動がどの半導体メーカーでもできるようにする。その統合作業にも着手し始めたと、Sawicki氏は言う。

Olympus-SoCは、Sierra Design Automation社が提供していたツールで、昨年Mentorが買収して手に入れたもの。Sieraのユーザーであった、STMicroelectronicsはMentorの検証ツールCalibreと組み合わせられるため、使いやすくなったとしている。タイミング解析アーキテクチャを導入、多数のプロセスコーナーや設計モードを最適化する。配線でもDFMを考慮した配線手法を採り入れている。さらに、低消費電力設計に用いられるマルチ電源にも対応できる。

MentorのCalibreは、方程式ベースのDRCファミリーとして改良し今回、2次元/3次元配線の検証ができるようになった。3次元は配線の段差やビアホール、コンタクトホールのなどのチェックに威力を発揮する。またメモリーの検証時間がかなり短縮したとしている。さらにCMPAnalyzerと呼ぶ平坦性の最適化も図れる。これはCMPとレイアウト密度の解析手法を使ってメタルの埋め込みなどをチェックする。Calibre nmLVSツールも搭載し、レイアウトと配置図形のチェックをチェックして修正できるという機能を持つ(ただし、市場で入手できるのは2008年後半)。

これらのツールを使って390万ゲートの競合他社の製品回路を65nmプロセスで試作評価してみたところ、競合他社と比べてクロックのばらつきは40%低減し、バッファとしてチップに搭載していた面積は50%減り、トータルの面積は18%削減できたという。ダイナミック動作時の消費電力は20%減少している。クロックスキューは40%減ったという。

また、配置、クロック給電、配線、最適化、DFMなどの処理をマルチスレッド・マルチコア方式で並列処理計算して求めるわけであるが、特別な高速コンピュータを製作するわけではなく、市販のLinuxベースのワークステーションで計算している。Calibreの方程式ベースの設計チェックツールは、近接チェッカーでは検出されないが、電流集中を起こしやすい程度に離れているコンタクトの位置も発見できるため、電流集中を防ぐことができる。モデルをこのような所にも立てて計算する。もちろんリソフレンドリなツールだけに配線が細くなりすぎているようなホットスポットを検出できることはいうまでもない。

また、論理テストのツールでは、更なる集積度向上によりテストデータの増加に対して、ATPGを圧縮する機能を搭載している。今は、TestKompress Xpressだが、2011年以降に向け、TestKompress In-SystemやTestKompress Low-Power Overdrive、さらに TestKompress Multicoreという三つの開発を同時に進めている。隠れて見えないシステマチックな欠陥を同定する診断アルゴリズムを開発、歩留りを向上できるとしている。