IntelがマルチコアプロセッサとコアごとのメモリーをTSVでつなぐシステムを発表

米Intel社は、3次元チップスタック実装がマルチコアプロセッサシステムのメモリーバンド幅を広げるのに有効であることを、ASET(超先端電子技術開発機構)主催のInternational 3D System Integration Conference 2008で示した。東京千代田区の一ツ橋講堂で開催された、今年の3D-SICは、基調講演を含め28件の講演発表と18件のポスターセッションがあった。

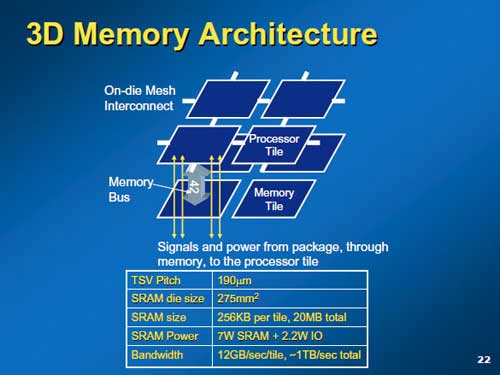

現在、メモリーのバンド幅がプロセッサのI/Oデータレートについていけないほど差がついてしまっている。この差を縮めようという発想がIntelの指向する3次元実装である。メモリーのバンド幅を広げるため単純に並列にデータを取り出すなら差動方式では400ピンものデータ線が必要になる。その原因の一つはI/Oラインの信号の遅れによる。信号波形は崩れ、すなわちシグナリインテグリティが悪くなるため、ノイズ対策はもちろんのこと、プリエンファシス、イコライザ処理などの波形整形処理が必要になり回路が複雑になってしまう。しかも分布定数回路的な電磁波としての反射を考慮しなければならない。3次元スタック実装でプロセッサのタイルとメモリーのタイルとの距離が近ければ、配線抵抗やインダクタンスの影響は無視できるため、シグナルインテグリティの設計が非常に楽になる。

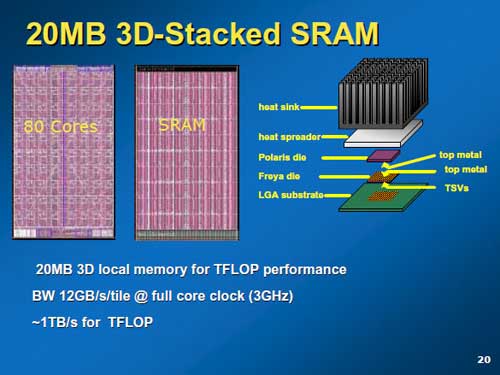

Intelが示したこの3次元実装システムは、80コアを集積したプロセッサチップの中のコア(タイルと呼ぶ)と20MバイトのSRAMチップを80ブロックに分けそれぞれのブロックをタイルとバスで結ぶというシステム構成である。メインメモリーとアクセスする前に、L1、L2キャッシュに加え、ローカルメモリーも配置することで、高速性を維持できる。

各プロセッサタイルとメモリータイルは42ピンの通常のバスで結んでいる。このバンド幅は、3GHz動作のフルコアクロックで1タイル当たり12Gバイト/秒となり、両チップ全体のバンド幅は、超並列コンピューティングにふさわしい1Tバイト/秒になる。SRAMの消費電力は7W、I/Oでのそれは2.2Wである。

80コアを搭載したプロセッサチップの大きさは、21.72mm x 12.64mm= 275mm2で、タイル一つの大きさは2.0mm x 1.5mmである。プロセッサチップは、65nmのCMOSプロセスで製造し、総トランジスタ数は1億個に及ぶ。チップ単体のパッケージだと、1248ピンのLGAに14層配線、343信号線を収容する。20MバイトのSRAMチップも同じ大きさの275mm2である。両者をつなぐTSV(through silicon via)のピッチは190μm。

積層構造としては、LGA(ランドグリッドアレイ)基板の上にSRAM、その上にマルチコアプロセッサチップ、さらに放熱板とヒートシンクを載せていく。両チップはフェースツーフェースで接続する。講演した同社Microprocessor Technology研究所のShekhar Borka氏は、これまでは配線で消費する電力は無視されてきたが、メモリーがDDR3へと高速になるにつれ、この消費電力改善は欠かせなくなるとみている。