ARMがIBMコモンプラットフォームとの共同開発の詳細を明らかに

英ARM社は米IBM社のコモンプラットフォームチームと共同でフィジカルIP製品を開発し、それをライセンス供与することを9月30日に発表していたが、その詳細をARMフォーラム2008で明らかにした。ARMのようなIPを供与するというビジネスが実際のファウンドリなど半導体製造チームと直接、手を組むという例はこれまでになかった。

ARMのフィジカルIP開発チームはかつて買収したArtisanのチームであり、Cortexシリーズなどのプロセッサコアだけではなく、IPそのものもロジックライブラリやメモリーコンパイラ、GPIO/SPIO、高速インターフェースIPなど多岐にわたるIP製品を持っている。IPコアは論理設計が終わるRTLレベルではなく配置配線を終えたフィジカルIPをシリコン上で動作を確認しなければユーザーに使ってもらえない。これまでの65nm、45nmで動作したからとはいえ、32nmあるいは28nmで動作するという保証は何もない。このため実際に32nm/28nmのプロセスを開発しているIBMのコモンプラットフォームのチームと一緒に動作を確認し、動作するIPをライセンス供与するというもの。だからこそ、フィジカルIPはプロセス技術と深く関係する。

ARMのプロセッサコアが、低消費電力の下での性能向上とチップ面積の低減に注力して開発されてきたと同様に、プロセッサ以外のフィジカルIPについても低消費電力の下で性能追求とチップ面積低減の追求が特徴となっている。豊富なIPライブラリを生かし、プロセッサからボンディングパッドまでSoCを設計することをARMは標榜する。

9月30日に発表した内容は、「32nmプロセスではHigh-kメタルゲート技術でトランジスタを設計し、それを2009年にフィジカルIPを提供できるようにしていく。しかもフィジカルIP群は28nmまでスケーリング可能にする」、ということだ。具体的には、45nmまでの従来プロセスではポリシリコンゲートのSiONゲート絶縁膜をベースにしたトランジスタのIPだったが、これをHigh-kメタルゲートの標準プロセスすなわちファウンデーションIPに変えていく。さらにはフィジカルIPを最適化し、RTLレベルのコアと実行可能なフローも最適化し、エンハンストIPへとさらに特長を出していく。このようにして、ARMゆえの最適な消費電力や性能、シリコン面積へと実現する。

一方のIBMは、これまでのアライアンスにおいてHigh-kメタルゲート技術を使った32nmのSRAMテストチップを作っている。SRAM回路はメモリーだけではなくロジックチップのレジスタやFIFOなどさまざまな一時記憶的に使われることが多いため重要な基本回路の一つだ。IBMの32nm技術は、High-kメタルゲートのほかに、先端の歪技術、配線用にはLow-k絶縁膜、高NA利用の193nm液浸リソグラフィなどから成る。この技術によって、45nmノードと比べ消費電力は40%削減しながら性能を30%上げることができ、しかもSRAMに適用すると読み出し電流、リーク電流、VtをポリSi/SiONよりも改善できるとする。しかもプロセスが単純になるゲートファースト手法を利用し、IPの共同開発によりできるだけすぐに32nm製品のシャトル生産を目指す。

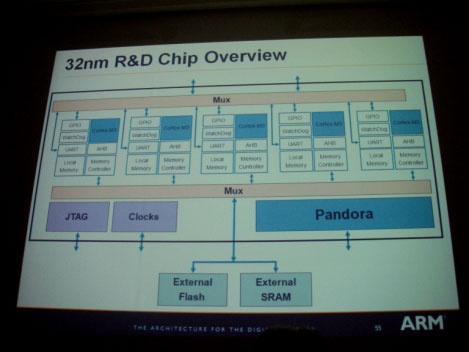

現在、デザインルールチェック、回路性能と消費電力について共同検討中であり、32nmのテストチップを使って現実的な設計を行っている。Cortex-M3コアとローカルI/O,メモリーを備えたプロセッサ5個と、Pandoraと呼ぶテストパターン回路、JTAG、クロックなどから成る。Pandoraには、レベル2キャッシュコントロールやレジスタからL2RAM、ALU、RAMからL/SレジスタなどのARM1176のクリティカルパスオシレータ(10~20ゲート分でリングオシレータ群を構成)、MOSFETアレイ、メモリーアレイ、寿命試験用構造などを含む。

ARMフォーラムではIBMからもコモンプラットフォームについての詳細が明らかになった。歪シリコン、Cu/Low-k材料、High-kメタルゲート、エアギャップなど将来につながる重要な技術を開発したIBMと、微細化技術でITRSよりも遅れをとってしまったチャータードセミコンダクタが追い付き追い越すために協力して始めたのがコモンプラットフォームプロジェクトだと同社の日本法人アカウントセールス部長の志澤弘は語る。

今、JDA(Joint Development Alliance)と呼ばれるチームは二つあり、先端半導体の研究開発(Advanced Semiconductor R&D)プロジェクトと技術開発(Technology Development)プロジェクトである。先端半導体研究開発は、ニューヨーク州アルバニーナノテクセンターで行われ、革新的な高集積デバイスとプロセス技術を開発する。アプライドマテリアルズとASML、東京エレクトロンの装置開発チームと、IBM、AMD、フリースケール、STマイクロエレクトロニクス、東芝、NECが参加している研究チームがある。より製品に近い技術開発は、IBMのイーストフィッシュキル工場を中心に複数の企業が共同開発するもの。バルクチームにIBM、チャータード、インフィニオン、サムスン、フリースケール、ST、東芝、NECが参加し、SOIチームにIBMとAMD,フリースケールが参加している。

もう一つのCDA(Common Platform Development Alliance)は製品に直結した技術プロジェクトで、マスクレベルのGDS II互換性のあるプロセス技術を開発する。バルクチームにIBMとチャータード、サムスンが参加し、SOIチームにはIBMとチャータードがかかわっている。開発はそれぞれ米国、シンガポール、韓国で行われている。