再配線用インターポーザーの導入により3次元TSV ICを極薄に

チップ間接続がこれからの3次元ICにますます重要になり、TSV(through silicon via)いわゆる貫通電極が今、注目を集めているが、接続の問題だけではなく設計の難しさが指摘され始めた。TSVでチップ間を3次元方向に接続すると、性能は20~30%向上し、ノイズの影響を受けにくいなどメリットは極めて大きい。しかし実用化までには問題が山積している。TSV電極を形成する時間が長いだけではなく、熱の問題などもこれまで指摘されてきた。最近、設計上の自由度が小さくなるという問題も指摘されている。

CEATECの会期中、10月1〜3日にかけてJissoフォーラム2008が同じ幕張にあるアパホテル&リゾート東京ベイ幕張ホールで開かれ、その解を模索した。メモリーとロジックICをTSVで接続するためには、それぞれの電極パッドの大きさと位置を統一しなければならない。インテルはSEMICON WestでチップのTSVの位置を同じにしようと呼びかけたといわれている。

接続位置を同じにするためには、複数のチップを縦方向に接続することを個々のチップ設計に予め盛り込んでおくことが望ましい。しかし、メモリーとロジックで同じ位置にTSVを設けることは設計上、大きな制約となり難しい。そこで、東京大学生産技術研究所の桜井貴康教授は、インターポーザーを介して各電極を接続しやすいように再配線する必要があると述べた。

これに対して、インターポーザーを導入するとコストアップになると、NECエレクトロニクスは敬遠する。

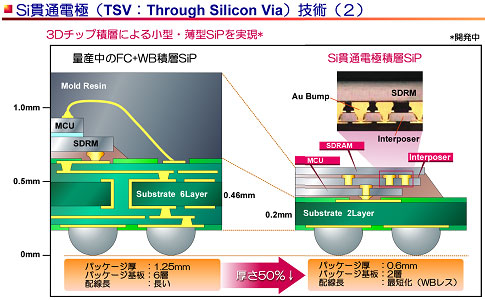

コストアップについては今後、詳細に検討する必要があるものの、ルネサステクノロジはインターポーザーをチップ間に入れても実装パッケージ基板を含めたトータルの厚さは、半減することを示した。同社は現在、量産中のマイクロコントローラMCUとメモリーSDRAMを積層し、ワイヤーボンディングで接続したSiPパッケージと比較した。量産のSiPパッケージでは、6層のプラスチック基板上にSDRAMをフリップチップで形成し、その上に絶縁シートを挟んでMCUを載せ、MCUの電極パッドとパッケージ基板の表面電極とはボンディングワイヤーで接続する。パッケージ裏面の半田ボールを含めたトータルの厚さは1.25mmである。

これに対して、現在開発中のTSVによる3次元積層ICでは、インターポーザーを入れて再配線してもトータルの厚さは0.6mmしかなかった。構造的には今度はMCUを下に置き、その上にインターポーザーを介してSDRAMを載せている。インターポーザーを入れても薄くなったのは、パッケージ基板の配線層数が従来の6層から2層に減ったためだとしている。すなわちインターポーザーの再配線によって下にあるパッケージ基板の配線層数を減らしたのである。パッケージ基板の厚さは従来の0.46mmから今回0.2mmに減少した。配線長はワイヤーボンディングではないため最も短くなったという。

このインターポーザーによる再配線手法は、3次元実装のTSVを推進する上で常套手段になるかもしれない。メモリーやロジックなどのチップの電極配線設計に負担をかけなくて済むためだ。ファブレス、ファウンドリ、IDMの半導体メーカーいずれもTSVのための設計を相手のチップの電極の配置、サイズに応じて変えることには難色を示すだろう。となると、インターポーザー設計サービスというビジネスが新たに生まれてくる可能性がある。