3次元SiP集積化技術がシステム問題取り組みに向かい始めた

シリコンチップを3次元に重ね合わせて、一つのICパッケージに集積する技術、3次元SiP技術が新しいフェーズに入った。TSV(through silicon via)と呼ばれる貫通電極、それに伴うエッチング、電極穴埋めといったこれまでの製造プロセスに焦点が当たっていた3D集積技術の応用が見え始め、設計や信頼性評価、テストへとシステム的な広がりを見せてきた。ASET(超先端電子技術開発機構)が主催したInternational 3D System Integration Conference (3D SIC) 2008においてこういった傾向が見えてきた。

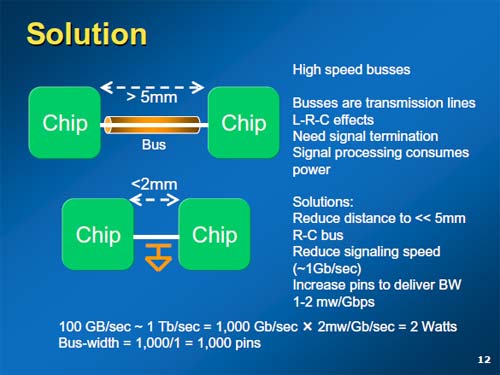

初日最初の基調講演で、米Intel社Microprocessor Technology研究所のShekhar Borkar氏は、3次元に集積することの最大のメリットがCPUやI/Oの高速のデータレートに対して、メモリーの遅いデータレート、すなわちバンド幅とのギャップを埋めるためのキーテクノロジだと述べた。しかもI/OピンではGbps当たりの消費電力はまだ大きいため、これも下げる必要がある。このための3D実装が決め手になるという。例えば、チップ間の信号は5mm以上離れるとインダクタンス成分が効いてきて分布定数的な振る舞いをするためインピーダンスマッチングの必要やシグナルインテグリティが問題となってくる。しかし、チップ間距離が2mm以下だとインダクタンス成分を無視でき集中定数回路で取り扱えるため、高速化に向くとしている。

さらにマルチコアやマルチプロセッサシステムではコアとL1およびL2キャッシュとのバンド幅を広くできるため、L2キャッシュとバルクメモリーとの間に3Dメモリーを搭載すれば、高速化だけではなく低消費電力化も可能になり、100Gバイト当たり25Wだったのが2W程度に収まると見積もっている。Intelは以前80コアの並列プロセッサを発表していたが、そのコアごとに256Kバイトのローカルメモリーを持たせるというアーキテクチャを3Dスタック構造で実現できる。ここに超並列マルチコアプロセッサのシステムが生きてくるとしている。

続いてベルギーIMECのEric Beyne氏は、3D集積化ではコストダウンが実用化のカギを握るため、3D実装のWLP(ウェーハレベルパッケージ)やワイヤボンドによる従来のスタック実装、TSVによる実装などの比較を行った。その結果、やはりTSVがコスト的に見合うこと、できるだけ貫通孔を小さくすることなどを述べた。TSVの最大の問題は、配線のルーティングであると指摘した。ルーティングはこれまで以上に複雑になり、へたをするとメタル層を追加したり、チップを大きくしなくてはならなくなる恐れさえあるとしている。TSVだけなら、半田ではなくCuを使った20μm程度の薄いウェーハの貫通ビアが高密度化できるという。

メモリーメーカーのドイツQimonda社Backend Innovation部門の主席エンジニアであるHarry Helder氏は、メモリー3D集積化のメリットはメモリーのバンド幅をさらに広げることだと述べた。やはりIntelと同様な考えでメモリーの3D化を進めている。同氏は、Qimonda技術の詳細は話せないとしながらもCuマイクロバンプが多ピン化の決め手になるとしている。これはCu電極の上にSnあるいはSn-Ag合金をコーティングしているが、固相反応で電極同士が結合するSOLID(solid liquid interdiffusion)技術と呼んでいる。

米UCLAのJason Cong氏は、放熱設計上でTSVは熱を逃がす重要な役割を果たすことをシミュレーションで検証し、フロアプランニングや多層スタック上のポートのパーティショニング、配線の折り返しデザインなどが熱抵抗を考慮した熱設計の指針になることを示した。

高速化に対しては、シリコンのインターポーザ(チップを載せる基板)の方向へ向かうことを沖電気工業や産業技術総合研究所などが指摘している。

ASETは平成19年度に「次世代三次元積層技術開発の先導研究」と称して3次元SiP集積化技術の調査を行ってきたが、その調査結果を3D-SIC終了後に発表した。その成果報告を受け、2008年度から3次元集積化技術プロジェクトの通称「ドリームチップ計画」をNEDOに申請し、現在検討中で本格的な3D SiP集積化技術プロジェクトがまもなく始まると見ている。