「システム的手法で消費電力を1/10〜1/20に低減する」、MentorのRhines氏語る

LSIの低消費電力設計が回路やデバイス・プロセスだけではなく、システム設計のレベルから必要になってきた。「消費電力の低減こそがいま、エレクトロニクス製品を差別化できるカギとなるパラメータだ」。米Mentor Graphics社CEOのWalden Rhines氏は、米国の広報会社Globalpress Connectionsが主催したeSummit2009において、このように述べ、システムアーキテクチャから低消費電力設計を行えば1/10〜1/20に低減できるとした。

Rhines氏は、いかに消費電力あるいはエネルギーの低減が重要か、低減しなければムーアの法則に見られるように1チップに集積されるトランジスタ数が増えていくため消費電力も同時に増加すると述べた。ちなみに2007年現在、すべての半導体チップに集積されているトランジスタ数は9.6×10の18乗個だとして、Pentium 4(Prescott)が5.7×10の10乗個使われている数に相当する。この数は原発3638基分、あるいは14億6000万世帯に相当するという訳だ。今のところ、トランジスタ数はムーアの法則というよりも毎年リニアに伸びている。今後はこれ以上の数字になる。

携帯電話機においてもスマートフォンだけではなく、MP3プレーヤー機能、カメラ機能などさまざまな機能が載るコンバージェンスの時代になっている。リチウムイオン電池のエネルギー密度の向上ペースはICチップの集積度向上のスピードよりも緩い。

一方で回路やデバイス、プロセスの世界を見ると、ダイナミックパワーはもはや変わらなくなってきた。クロック周波数を上げられなくなってきたからだ。しかしドレイン-ソースのリーク電流はトランジスタ数の増加と共に増える傾向にある。マイクロプロセッサはすでに性能よりも低消費電力化への対応が進んでいる。

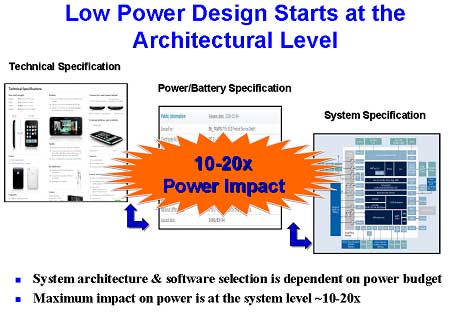

そこでさらに消費電力を下げるために、もはやシステム設計、アーキテクチャ設計から消費電力を考慮していかなければならない。特にシステムアーキテクチャとソフトウエアの選択が消費電力の低減に大きく寄与するとした。Rhines氏は「iPhoneの不満はバッテリ寿命が短いこと。だからデザインによって解決する」と述べ、「パワーがデザインをドライブする」と強調した。

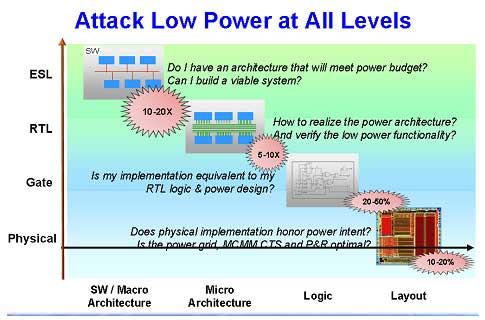

システム設計では、全体をどうパーティショニングするか、パワーをどう定義するか、ということが深く関係する。にもかかわらず、「これまでのシステム設計者が消費電力は自分の問題ではないとばかりに回路技術者、デバイス技術者に渡してしまった。これはいまだにシステム設計がマニュアル作業だからそのようになってしまう」と言う。PCB上でパーティショニングをうまくやることでシステム全体の消費電力は1/5〜1/10に減るとみている。

さらにPCB上の部品をCPU、GPS、PMUなど必要なキーコンポーネントにまとめると20%〜50%は減る。そしてLSI設計でICブロック設計のパーティショニングで10〜20%削減できる、とした。

LSI設計レベルでは、次世代LSI設計に関して述べ、各レベルにおける問題を提起した。プロセスに近い物理設計では、プロセスコーナーをワーストケース設計(ワーストコーナー)でやってきたが、微細化が進むにつれ、コーナーの数は急増する。ここでコーナーと称しているのは、プロセスのばらつきを考慮しなければならないカギとなるプロセスのこと。例えばゲートしきい電圧Vthはハイエンド素子、ローエンド素子で±5〜10%をバラつきとしてきたが、Vthのようなカギとなるプロセスパラメータ、すなわちコーナーの数が増えていく。130nm設計では4コーナーだったのが、90nm設計では10コーナー、65nmだと21コーナー以上にもなるという。さらにタイミングマージンも加わる。それらを同時に解き、検証しなければ正常動作は期待できない。

それらを解決した上で、ネットリストデータから物理合成、クロックツリー合成、配線設計、そしてGDS II出力する間にも、多数のVDD電源の流れや電圧、周波数の最適化、アダプティブなスケーリング、クロックツリーの再構成などのダイナミックパワーの低減、マルチVthやパワーゲーティング、バックバイアスなどのスタティックパワーの低減などが必要になる(下図)。

上位設計レベルでは、ESLレベルがRTLレベルやPHYレベルなど下位レベルへどう影響するのかを調べることが大事、だという。このレベルでは、UPF(Unified Power Format)形式に従って検証を行う。UPF形式はかつてTI、ノキアとメンターが共同で開発し、シノプシスと標準化を決めたフォーマットのこと。まずすべてのパワーに関係する場所を見つけ、データリテンションが適切か、リセットできるかなどを検証する。パワーに関係するプログラムが成立しているかどうかを全体に渡ってカバーする。このようにしてパワーを意識した設計をシミュレーションしながら検証していく。

PCB上ではパワーインテグリティを確認し、例えば配線が狭すぎてノイズが載っていないかどうかなどを解析し確認する。PCB上では熱解析も行い、部品の配置が適切かどうかを調べるためホットスポットを見つけ、それを修正していく。

OSレベルでもパワーを意識したRTOS(リアルタイムOS)とそうではない汎用のLINUXを比べると、パワーを意識したRTOSだと消費電力は使用するメモリーにもよるが、5〜11%削減できるとしている。

LSI設計の例として802.11のMACプロセッサのパワーをハードウエアリッチ、ソフトウエアリッチ、シングルバス、ダブルバスなどについての評価例を紹介した。その結果、シングルバスですべてハードウエアで実現すると380.7mWで、ダブルバスを使いいくつかの機能をソフトウエアで実現する場合は766.8mWも電力を食うことを見せた。

要は、チップ面積と消費電力、性能の最適化がIPブロックだけで最適化していても、システム全体で最適化できているかどうかわからない。RTLレベルで設計していても単なるローカルな最適化かもしれない。しかし、「物理設計を駆使してグローバルに最適化すれば消費電力を20倍も下げられる。そのためには物理設計をもっと自動化することがカギとなる」とRhines氏は結んだ。