10μm径で深さ125μmの貫通電極をAviza社が試作

米Aviza Technology社は、3次元SiP製造に向けた貫通孔形成プロセスに注力している。セミコン台湾において同社が出展した理由はまさにこの点にある。つまり台湾では今、LSIパッケージメーカーが貫通孔形成技術の開発に注力しているからだ。

13日午前中の基調講演で述べた、台湾ASE グループ社ジェネラルマネジャー兼チーフR&DオフィサーのHo-Ming Tong博士の内容を裏付けるかのように、この貫通孔形成にはパッケージングメーカーだけではなく、メモリーメーカー、材料メーカーまでもがコラボレーションしている。

この貫通孔はメモリーチップを何枚も重ねるのに威力を発揮する。DRAMだけではなく携帯電話に応用されているようにDRAMとフラッシュメモリーを重ねる応用も多い。1つのLSIパッケージに入れたメモリー容量をパッケージを厚くすることなく簡単に増やせるからである。応用は携帯電話にとどまらず、PDAやiPod、iPhoneなど映像や画像を取り込む携帯デバイスなどにも需要がある。メモリー容量は多いのに越したことはない。

この貫通孔をウェーハプロセスの最後に形成する場合にはリスクが高くなる。失敗が許されない。かといって最初からウェーハを削るわけにはいかない。割れるリスクが伴うからである。Avizaのプロセスはウェーハプロセスの比較的始めの段階で深い溝を掘り、その中に金属を埋め込み貫通電極を形成するもの。すでに、直径10μmで深さ125μmという極めてアスペクト比の高い貫通孔を形成している。貫通孔は当然ながら上から下まで均一な直径で形成されなければならない。抵抗が高くなっては意味がないからだ。

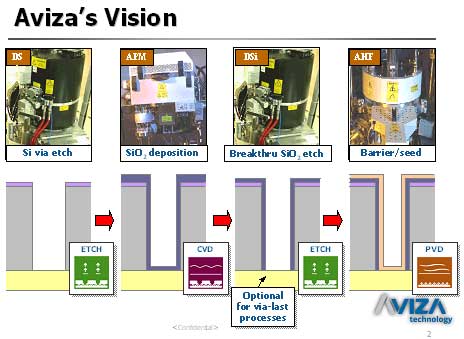

貫通電極は、エッチング、CVD、エッチング、バリヤメタル堆積などの工程を経て形成される。特に深いエッチングを行った後は、コンフォーマルなCVD形成やPVD技術が重要になる。深いエッチングにしても、125μmととてつもなく深い溝の形成には、単純なエッチングでは形成できない、と同社PVD,CVD&エッチング製品グループ担当副社長兼ジェネラルマネジャーのKevin T. Crofton氏は言う。エッチング速度を確保しながら、エッチングとデポジションを繰り返しながら穴を掘って行くのだという。

この貫通孔の形成は単なる実験ではない。パッケージングアセンブリメーカーと、IDMやファウンドリなどの半導体メーカーともコラボレーションして、要求仕様を聞いている。Crofton氏は、今LSIパッケージングの80%はワイヤーボンド技術で電極を結んでいるが、5〜10年後には50%が貫通電極になるとみている。