ラピダス、RISC-VのTenstorrent社と提携、最初の顧客になるか

先週、ラピダス社が顧客獲得に動き出した。日本時間11月14日に米国シリコンバレーに営業拠点を設置することを表明した後、16日の日経にはRISC-Vプロセッサを手掛けるカナダのファブレス半導体Tenstorrent社と業務提携すると報じられ、17日は2nmロジック半導体IPのパートナーシップで合意したとラピダスが発表した。さらにLSTC( 最先端半導体技術センター)がCEA-Letiと1.4nmノードのプロセス開発で合意した。

ラピダスは、2023年度内に米シリコンバレーに営業拠点を設置することを13日(米国時間)表明した、と15日の日経が伝えた。米国に出張中の小池淳義社長が米国で開かれた半導体関連の幹部会合で明らかにしたようだ。27年に量産予定の半導体顧客を開拓するための拠点となる。この会合は、経済産業省が13日、「インド太平洋経済枠組み(IPEF)」の閣僚会合に合わせて開いたという。

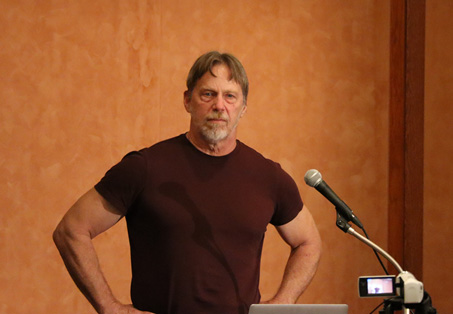

図1 Tenstorrent社CEOのJim Keller氏 RISC-V Day Tokyo 2023にて筆者撮影

16日の日経はラピダスがTenstorrent社と業務提携すると報じたが、正式には17日にラピダスがTenstorrentと2nmロジック半導体をベースにしたAIエッジデバイス領域での半導体IPのパートナーシップに関して合意したと発表した(参考資料1)。Tenstorrent社は、AMDのAthlonマイクロプロセッサやAppleのA4、A5などのアプリケーションプロセッサを設計してきたCPUの天才エンジニア、Jim Keller氏(図1)がCEOを務める会社。

Jim Keller氏は現在、RISC-Vプロセッサを基本としたAIチップを開発中だ。ニューラルネットワークモデルの演算に沿ってデータフロー型アーキテクチャを基本とするプロセッサで、エッジAIでの学習や推論に最適なプロセッサを構成している。これまでも3種類の機械学習(ML)向けチップを提供してきたが、2024年以降はMLチップレットとCPUをセットにしたAIアクセラレータを計画中。もちろんLLM(大規模言語モデル)モデルに適したエンコーダー回路を組み込んだ生成AI向けのチップも開発中だ。つまりエッジからクラウド用のAIまで揃える計画だ。

2023年には6nmプロセスノードのMLチップをリリースするが、ラピダスが量産する頃には、2nmプロセスノードのチップに期待しているのであろう。AIアクセラレータチップも、CPUチップもRISC-Vアーキテクチャで構成する。しかも基本的なチップ構成を数十個、数百個並列動作できるような拡張性(スケーラビリティ)を備えている。ラピダスの小池淳義社長は「Tenstorrentが当社の最初の顧客になることを期待する」と語ったと18日の日経が報じた。

ラピダスは2nmプロセスノードのGAA(Gate All Around)トランジスタのICを量産するファウンドリを目指しているが、2nmの先には1.4nmがロードマップに乗っている。そこで、1.4nmノードの開発にも着手するため、半導体研究開発組織であるLSTC(Leading-Edge Semiconductor Technology Center)は、フランスのCEA-Letiと提携した。LSTCにはラピダスの他、東京大学や理化学研究所、NIMS(物質・材料研究機構)などが名を連ねる。Letiと14.~1.0nmのトランジスタを共同開発する。現在のロードマップではnチャンネルGAAFETの上にpチャンネルGAAFETをスタックするCMOS構成のCFETトランジスタが提案されている。

参考資料

1. 「Rapidus、Tenstorrent社とIPのパートナーシップで合意」、ラピダスニュース(2023/11/17)