プリント基板と半導体が接近、先端パッケージに注力する太陽HD

プリント回路基板のソルダーレジストの最大手である太陽ホールディングスが半導体分野に参入する。それも先端パッケージのインターポーザ技術への応用を狙ったソルダーレジストとなる。ソルダーレジストはプリント基板上の緑色した樹脂で、半導体などの部品を接続する金属電極以外の全てを保護するという役割を持つ。

太陽インキ製造が持ち株会社である太陽ホールディングス(HD)となったのは2010年。以来、国内で6社を有するほか、海外法人を9社持っている。事業の中核は、ソルダーレジストで最大手だが、AppleのiPhoneに採用されたことで大きく成長した。プリント基板業界では有名な話だが、AppleのCEOだった故Steve Jobs氏がプリント基板上には黒い保護膜にこだわり、黒いソルダーレジストを開発できた太陽インキの製品を用いたことが最近の成長の原点となっている。

ソルダーレジストと言えば、半導体業界の方にはフォトレジストをイメージしてしまうが、フォトレジストとの最大の違いは、パターニングした後もレジストを除去せずに残すこと。残ったソルダーレジストが保護膜となる。また、ソルダーレジストを硬化させた後、ハンダの浴槽に浸けても電極金属部分にハンダが付くが、それ以外の領域にはハンダは付着しない。このため、ソルダーレジストに覆われた部分が配線の保護膜となる。このため絶縁膜の信頼性が問われることになる。

プリント回路基板では、もともと配線幅が数百µmと半導体の配線幅の1µm以下とは全く違い、印刷技術を使っていた。しかし、IntelやSoCメーカーのチップのパッケージがリードフレームではなくプリント基板を使うようになった頃から、100µmから50µmへと次第にプリント回路の配線幅の微細化が進み、半導体のそれに近づき始め、印刷からフォトリソグラフィ技術へと移行してきた。そして、先端パッケージのサブストレートやインターポーザなどの配線幅となれば数µmレベルへと微細化し、半導体プロセス技術に近づいてきた。

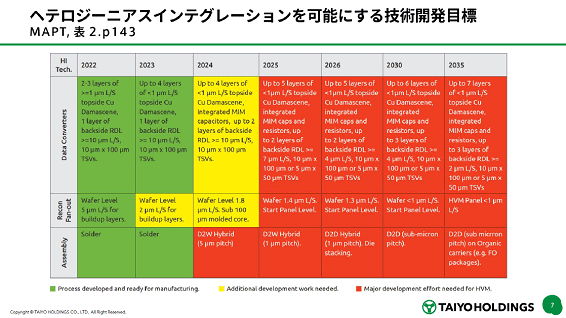

図1 SRCが発表したMAPTロードマップの一部 出典:SRC、太陽HD

米SRC(Semiconductor Research Corp.)は、昨年MAPT(Microelectronics and Advanced packaging Technologies)ロードマップを発表(参考資料1)、3D-ICや先端パッケージの将来への道筋をつけた(図1)。2023年までのロードマップとなっている。これによると配線幅と配線間隔(L/S)では1µmで4層、裏面再配線層1層が10µmというプロセスが生産準備段階に来ているという。しかも、銅配線は従来のメッキではなく半導体で使っているダマシンプロセスに代わっている。

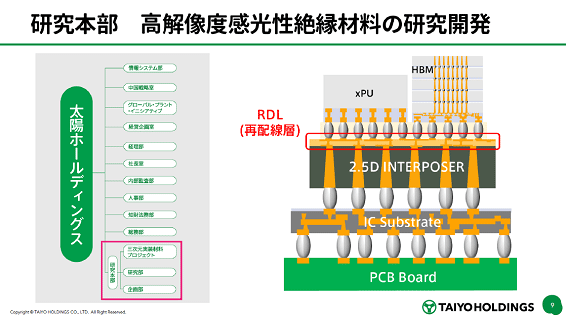

図2 インターポーザの再配線層材料に注力 出典:太陽HD

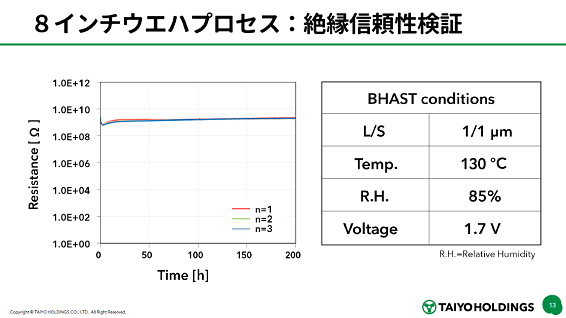

太陽HDでは、三次元実装材料プロジェクトという組織を作り、再配線層RDL(Re-Distribution Layer)における高解像度の感光性絶縁材料の開発に力を入れ始めた(図2)。このほど8インチウェーハで21個のチップ実装領域のブロックを作り、L/Sが1µmのパターンを描く実験を成功させている。さらにこの8インチウェーハの絶縁試験も行い、バイアス電圧1.7V、130°C、相対湿度85%の高温高湿バイアス試験で200時間まで絶縁性が保たれているという結果を得ている(図3)。

図3 高温高湿バイアス試験では絶縁性の劣化は見られない 出典:太陽HD

太陽HDは今後、300mmウェーハでの検証実験に取り組んでいく。さらに、世界的な半導体研究所であるベルギーのimecの3Dプログラムに参加し、RDL技術の微細化の共同開発に着手したという。

参考資料

1. "Microelectronics and Advanced Packaging Technologies Roadmap", SRC