急速に広がっているオープンスタンダードのRISC-Vコア

RISC-V(リスクファイブと発音)が急速に広まってきた。データセンター向けのアクセラレータやAIチップ、セキュリティ強化型のアーキテクチャ、クルマ用コンピュータのプラットフォーム、あるいはマイコンなどさまざまなコンピュータのプラットフォームとして広がりを見せている。オープンスタンダードは根底にあるからだ。

コンピュータは、基本的に一つのハードウエアプラットフォームを作り、その上でソフトウエアで差別化を図るマシンである。「オープンスタンダードの規格を共に作る人たちの精神がRISC-Vにはある」。こう語るのはRISC-V Internationalの日本代表である河崎俊平氏。同氏はかつて日立製作所でSHマイコンを開発していたトップエンジニアだ。

RISC-Vアーキテクチャでデータセンター向けのコンピュータチップを開発しているEsperantoやTenstorrentの狙いは、NvidiaのGPUの1/10〜1/4という低い消費電力のAIチップの開発を目指すためだ。「最先端のGPUであるH100チップをもし100万個使ったら生成AIシステムの消費電力はべらぼうに大きくなり、原発1基や2基では対応できなくなる」と河崎氏は言う。これは2〜3年先には現実的になってくる。

もともとRISC-Vは、カリフォルニア大学バークレイ校のDavid Patterson教授とKrste Asanovich教授から開発したフリーのCPUコアであり、GitHubにも登録されたオープンなCPUアーキテクチャである。しかも命令セットは本来のRISCアーキテクチャのように47命令しかない。これにカスタム命令を追加するのである。このため、カスタムCPUを設計しやすい。すでにルネサスは独自設計のRISC-V CPUコアを開発し、SoCを設計していくレベルに達している。

2024年1月中頃、東京大学で開催されたRISC-V Dayでは、RISC-Vを手掛けているさまざまな企業が登場した。データセンター向けのアクセラレータを開発しているVentana Micro Systems社は、RISC-VのCPUコアだけではなくチップレットやSoCも開発している。2018年に設立され、シリコンバレーに拠点を置く同社の中核メンバーはArmの64ビットアーキテクチャを開発してきたエンジニア集団だ。

チップレットを念頭に置くスタートアップであるからこそ、ダイ2ダイ(D2D)といった3D-ICのインターフェースを作り、チップレットの標準規格を目指すUCIeに準拠するチップレットを提供できるようにする。狙いはやはりAIで、生成AIからエッジAIまでをカバーする。現在4nmプロセスで設計するCPUコア「Veyron 2」を開発中だ。 AMDのEPYCシリーズやIntelのXeon、Arm 64よりも消費電力当たりの性能を上げる設計となっている。GPUも搭載できるように共有キャッシュのコヒーレンシー(CPUもGPUも同じメモリをアクセスできること)を高め、コヒーレントなNoC(Network on Chip)バスで192コアを動作できる。

天才CPUデザイナーのJim Keller率いるTenstorrentは、Jimと同様AppleでSoC「Aシリーズ」を設計していたWei-han Lien氏がチーフCPUアーキテクト兼シニアフェローとして講演した。「なぜRISC-Vか」という問いに対して以下のように語っている。「各国の専門家と話をしてきて半導体は極めて重要な部品であるという認識で一致した。CPUは水や電気と同じようなインフラになった。しかもAIは今後さまざまなところに広がる重要な技術であるから、AI+CPUの半導体チップを作ることを目指している。それも単価10ドルと極めて安いチップを目指す。そして、AI+CPUチップはエッジからハイエンドまでカバーするためRISC-Vが最適だ」。

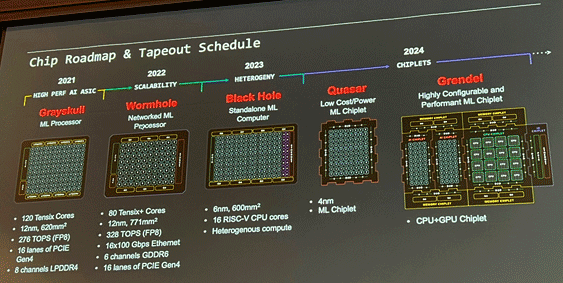

図1 Tenstorrentの高性能なRISC-VコアAscalon

現在、高性能なRISC-VコアとしてAscalonを設計(図1)、さらに低消費電力の4nmチップレットQuasarと、CPU+GPUのスケーラブルなチップレットとしてGrendelを開発中で(図2)、今年度末にテープアウトする予定だ。多数のIPコアを接続できるようにするためNoCマネージャーを設計、Texsixコア1個から数千チップまで拡張できるように入出力を設計している。Lien氏にビジネスモデルについて質問すると、当分はCPU+AIチップレットをチップレットやチップビジネスの核とするが、将来は(もっとAIモデルの学習を短縮できる)コンディショナルコンピューティング(ネットワークの一部だけを選択して動作させるコンピューティング手法)に進むだろうと答えた。

図2 TenstorrentのCPU+GPUコアのGrendel

EDAのトップベンダーであるSynopsysは最近、Imperasを買収、RISC-V技術を手に入れた。以前に買収したARC International社のCPUコアに加え、ARC命令を拡張命令に加えたRISC-Vバージョンも提供し始めた。

中国のファブレスGagaDevice社はこれまでArmベースのマイコンを設計してきたが、ここにRISC-Vコアも製品ポートフォリオに加えた。RISC-Vマイコンは、液晶コントローラやコーヒーマシン、電子タバコなど民生向けの製品が多いが、最近は自動車関係の顧客が増えてきたとしている。

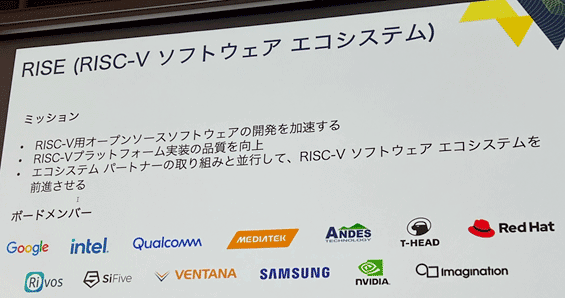

図3 RISC-V向けソフトウエアを開発するエコシステムRISE(RISC-V Software Ecosystem) LINUXファンデーションのプロジェクトの一つ

「これからはRISC-Vのエコシステムをどう広げていくかが問われている。ソフト会社(図3)やファウンドリなどすそ野を広げていくことが普及につながる」、と東大大学院工学研究科システムデザイン研究センター兼電機系工学専攻の池田誠教授は締めくくった。