ファウンドリが次々とシミュレーションベンダーと組む理由

これまで半導体産業とは縁が薄かった、3D-CADとシミュレーションのベンダーが積極的に半導体産業にやってきている。2.5D/3D-ICやチップレット実装などで数値計算シミュレーションが設計時に欠かせなくなってきたからだ。シミュレーションベンダーのAnsysがTSMCやGlobalFoundries、Samsungファウンドリ部門、Intelファウンドリ部門、UMCなどと次々と提携を発表している。

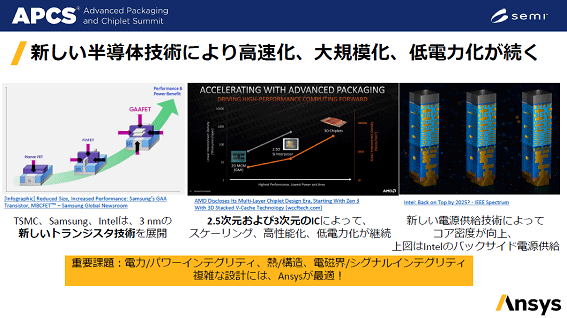

図1 半導体実装が3次元化し、シミュレーションなしに最適解が得られなくなる 出典:Ansys

とりわけ、TSMCはEDAベンダービッグスリーとはエコシステムを形成しているが、ここにAnsysを加えた。TSMCは先端パッケージング技術でシミュレーションベンダーの重要性を知っているからだ。半導体技術はプレーナトランジスタからFinFETやGAA(Gate All Around)FETのように3次元化へと進展し、配線層でさえ信号層と電源層をウェーハ張り合わせ手法などで構成するような方向に向いているように、モノリシックICでさえ3次元化の方向が明確になっている(図1)。ましてや2.5Dや3DのICとなるとチップをTSV(Through Silicon Via)などで重ねていくようになる。生成AI需要で急速に需要が高まっている、3次元構造のHBM(High Bandwidth Memory)では、複数のDRAMチップとコントローラチップを重ねているが、ここでは電力からの熱によって機械的な応力が発生する。チップや基板での反りや割れが生じるリスクが出てくる。

電極構造でもCuピラー同士をマイクロバンプなどで接続しているが、熱応力を解析するためにバンプの形状シミュレーションが必要になる。このバンプがエレクトロマイグレーションを起こすとも言われている。さらに、寄生効果によるシグナルインテグリティも問題になってくる。高速スイッチング動作させると数百、数千にもなるTSV電極による電磁界カップリングが起き、動作が不安定になる。

チップを実装する前に、シミュレーションで確認する必要がある。熱や電磁界、機械歪などの物理現象をモデル化してシミュレーションする専門家が欲しい。Ansysがこの専門家である。「推量ではなくシミュレーションを正しい方法で行うことが重要」とAnsysのChief Technologistを務めるChristophe Bianchi氏(図2)は述べる。

図2 Ansys社 Chief TechnologistのChristophe Bianchi氏

Ansysは昔から、さまざまな物理現象に対してモデルを立て方程式で計算処理してきた。ところが、半導体チップ上ではさまざまな小さな場所での電力消費や、時間的に場所の移動など複雑な系でのモデルを立てようとするとその次元が4、5、6次元へと増えていく。こうなるとAnsysといえどもモデルを立てることが複雑になる。複雑な系では数10年前からモンテカルロ手法などが使われてきたが、Bianchi氏によると、「モンテカルロシミュレーションだとせいぜい4次元程度しか計算できない。さらに複雑になると威力を発揮するのがAI/ML(機械学習)だ」、と言う。

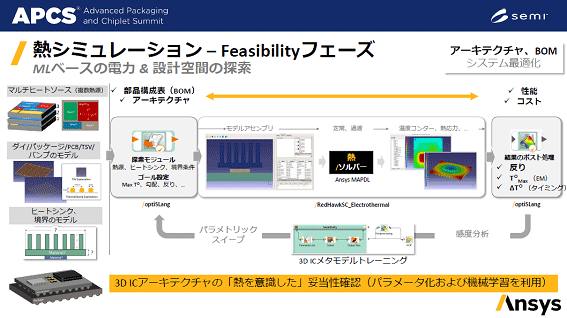

これまでのシミュレーション設計手法を考え直し、MLを活用しなければ熱やシグナルインテグリティを考慮した回路設計はできなくなるとBianchi氏は述べる。MLで入出力関係を簡素化し、メタモデルを作って学習を繰り返す(図3)。特に3次元ICでは熱の問題が重要になると、3次元ICを手掛けるファウンドリ関係者は述べている。

図3 ML(機械学習)を利用して複雑な関係性を簡素化する 出典:Ansys

Ansysは、5つのコアコンピタンスというべき柱(ピラー)を持っている。すなわちマルチな物理学やさまざまなモデル、HPC(High Performance Computing)、AI/ML、クラウドやユーザーエクスペリエンス、そしてデジタルエンジニアリングの5つだ。クラウドやMLなどを駆使して最良のソリューションを提供するとBianchi氏は胸を張る。