40万ロジックセルで6mm角のパッケージのFPGAをLatticeがリリース

「CPUを集積したSoCではなく、SoCに独自機能を追加するため専用回路を設けたいが、小型で数万ゲートくらいは欲しい」、という要求に合ったFPGAをLattice Semiconductorがリリースした。しかも256ビットの暗号化できる簡単には書き換えられないセキュリティも導入している。先端のクルマやIndustry 4.0向け産業機器、通信基地局などに向く。

図1 パッケージサイズが同等品の1/3と小型で、入出力データ速度が1.5Gbpsと高速 出典:Lattice Semiconductor

Latticeのビジネスはかなりユニークだ。XilinxやIntel(旧Altera)のような超高集積化、超高機能化は狙わず、やや高機能化程度の応用で独自の専用回路を設計したいユーザーに向けている。今回の製品「Certus-NX」シリーズは、XilinxのArtixs-7やIntelのCyclone Vなどに相当する製品だが、競合メーカーはもっとハイエンドの製品開発に集中させており、従来製品のまま小型化や高機能化、高性能化をしていない。ここにLatticeの狙う市場がある。

SoCを設計しようとすると、CPUの選択、ソフトウエア開発、周辺機能の選択と集積化、などシステム設計から始めなければならずそれだけでも2〜3年かかってしまう。もちろん、コストも高い。そこで、SoCはそのままにして、追加機能をFPGAによる専用回路で実現するという手法はスマートフォンをはじめ、いろいろな応用で使われるようになってきた。

Certus-NXシリーズは、ICパッケージサイズが同等品の1/3、I/O数が1mm2当たり2.3倍と高密度で、差動I/Oのデータ速度が1.5Gbpsと70%高速になっている。ロジックサイズは17K〜40Kのロジックセルやメモリなども集積しているほかに、5Gbpsのレーンを持つPCIeバスや、18×18ビットの乗算器を2個集積したDSP、ADコンバータなども内蔵している(図2)。

図2 Certus-NXの内部構成 出典:Lattice Semiconductor

技術的には、28nmルールのFD-SOI(Fully Depleted Silicon on Insulator)プロセスを使っているため、SER(ソフトエラー率)が従来の1/100、消費電力は1/4と小さい。性能は28nmのFD-SOIは14/16nmのFinFETプロセスとほぼ同じと言われている。

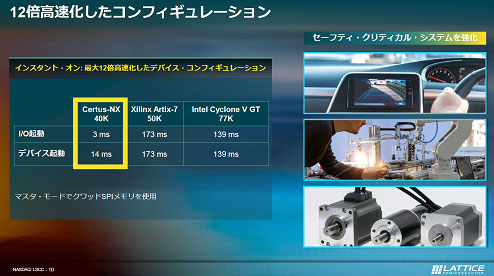

FPGAはロジックを構成するための配線接続のスイッチの役割をSRAMが果たしているが、起動時には電源を入れるとすぐに外部フラッシュなどのメモリからコンフィギュレーションなどのデータをSRAMにロードしていく。従来のFPGAだとデバイスを起動するのに100ms以上も時間がかかるが、Certus-NXでは14msしかかからない(図3)。

図3 コンフィギュレーションにかかる時間を1/12に短縮 出典:Lattice Semiconductor

新製品では、インスタントオンを実現した。まずI/Oの構成を先にしてから内部のコンフィギュレーションへとロードするようにした。起動時には電源制御のHとLを3msでI/Oを設定する。そして内部の接続情報のデータ量を減らしてコンフィギュレーション時間を短縮した。しかも、データをロードするためのインタフェースSPIを4本並列にしたQuad SPIを使うことでロードする時間を短縮した。

そして、セキュリティを確保するため、256ビットストリームのECDSA(楕円曲線暗号を用いたデジタル署名アルゴリズム)で署名し、その署名するのに用いた秘密鍵をユーザーが保持しておく。FPGA側では、ユーザーの署名をECDSAで検証するが、その場合に公開鍵を使って暗号を解く。公開鍵はチップ内のOTP(One Time Programmable ROM)に格納する。この暗号化によって、署名されていない人はFPGAを書き換えることはできない。