プラズマダイシング工程以降でパナソニックとIBMが協業

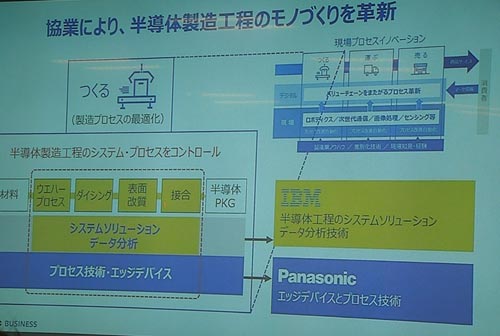

パナソニックコネクティッドソリューションズ(CNS)社と日本IBMは、半導体後工程の分野で提携した(図1)。これは、パナソニックの持つ後工程のプラズマダイシング装置とプラズマクリーナ装置にIBMのFDC(故障予知管理)ソフトウエアを組み込んだ装置システムの開発を目指すもの。

図1 協業するパナソニック(右2名)と日本IBM(左2名) 出典:パナソニック

パナソニックは、AEC/APC Symposiumなどでこれまで発表があったように、プロセス装置のデータを収集・管理・分析してフィードバックおよびフィードフォワード的に制御することで歩留まり向上、生産性向上につなげてきた。パナソニックCNSは、これからの3D-ICやFOWLP(Fan Out Wafer Level Packaging)などの前工程と後工程の中間工程ではプロセスのノウハウを生かした装置のフィードフォワード制御や故障予知などが求められると判断した。

半導体製造のデータ分析ではIBMはこれまでプロセス工程での実績があり、特にMES(Manufacturing Execution System: 製造実行システム)ソフトウエアでは市場シェアは50%も握っているという。IBM本社は半導体プロセス工程のAPC(Advanced Process Control)やFDC(Fault Detection and Classification)などのデータ解析システムでも外販実績が豊富だ。

パナソニックが得意とする後工程装置(図2)でも、3D-ICやFOWLPなどのパッケージング工程はウェーハそのものを加工するため、前工程で実績のあるIBMと組んだ。IBMは、AIチップをはじめとするハイエンドチップの試作ができるように製造技術の手を緩めてはいない。ただ、量産工場はGlobalFoundriesに明け渡し、量産技術を手放している。

図2 今回の提携では完成したウェーハをチップに切り分ける後工程で適用する 出典:パナソニック

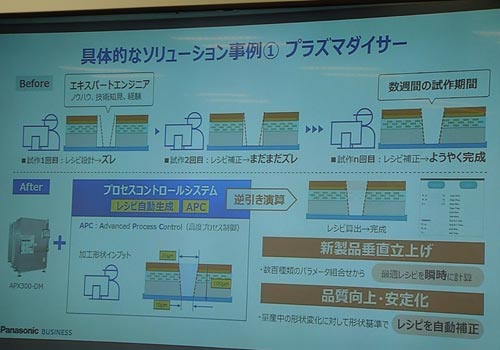

パナソニックが製造するプラズマダイシング装置では、チップ間隔20µmで厚さ100µmのウェーハをダイシングするが、ウェーハ上のチップ間隔20µmでウェーハの底(裏面)では10µmと間隔を短縮するようなテーパー形状が望ましいとされている(図3)。このためにダイシングするチップ断面は垂直に切るのではなく、傾斜がつくようにプラズマエッチングの条件を制御する。これまではエンジニアがテーパーをつけるのに試行錯誤を繰り返しながら、その条件を決めてきたが、これからはプロセス条件でレシピを算出してカットしていく。このためには、数百種類のパラメータの組み合わせから最適なレシピを瞬時に算出していく。この算出を行うための分析ツールをIBMが手掛けていく。

図3 プラズマダイシングでチップ間隔10µmでチップを分離する 出典:パナソニック

また、プラズマクリーナでは、プラズマ放電が不安定になり異常放電が発生するようになると、製品は不良品になる。正常と異常のデータを大量に取っておけば後で分析に使える。装置の状態をスコアにしてデータ分析できるような形にしておく。データが分析できると、装置がどのような状態になると故障に至るのかを知るために、データパターンを学習しておくと、故障予知につながる。データを分析するのがIBMの役割だ。

想定顧客はOSATや後工程を持つ半導体メーカーだ。装置メーカーとしてパナソニックは、装置を販売してお終いではなく、サービスを含めたビジネスモデルを考えていく。一定の開発の進歩が見えたら、長期的に顧客との関係を保つビジネスへつなげていきたいとパナソニックCNS社社長の樋口泰行氏(図1の右から2番目)は述べている。