65nmの次は28nmデザインを推進するラティス、日本のファウンドリは市場喪失

米ラティスセミコンダクター(Lattice Semiconductor)社は、現在主流の65nmプロセス製品で富士通とセイコーエプソンをファウンドリとして使っているが、次は45nm/32nmをスキップしていきなり28nmプロセスへと向かうことを明らかにした。日本の半導体メーカーは28nmを開発していないため、ファウンドリとしての顧客を失うことになる。

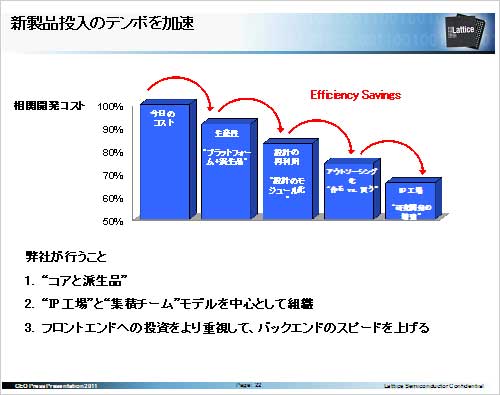

図1 ラティスの製品を早く出荷する仕組み 出典:Lattice Semiconductor

ラティスがローエンドとミッドレンジのFPGA市場へ乗り出すことはすでに伝えたが(参考資料1)、ミッドレンジではやはり微細パターンを使い、高性能・低消費電力の低コスト製品を作るための28nmプロセスをラティスは求めている。同社CEOのDarin Billerbeck氏は、「現在、世界ではファウンドリ3社が28nmプロセスを開発している。決め手となるのはコストであり、生産できるというコミットメントである。それを実現できるファウンドリを選ぶ」と言う。ファブレスだからこその強みがここにある。現在の65nm設計の量産チームとは別に、28nm設計のためのR&Dチームがすでにいる。

インテル、ザイログを経て昨年就任したCEOのDarin Billerbeck氏が率いる新生ラティスが特長とするのは、革新的な新製品をどこよりも早く出すこと。5月24日の記者会見の中で、Billerbeck氏は何度も「Go fast」あるいは「Run fast」という言葉を使った。そのためにIPを活用しFPGAそのものからSoC的なアプローチを進めていく。特にFPGAのビルディングブロックを推し進める戦略だ。IPライブラリを自社開発し、IPの中でもインターフェース周りのPCIeやUSB3.0のようなインターフェースIPを揃えていく。FPGAだけであれば設計やソフトウエアの再利用は難しいが、IPやビルディングブロック方式なら再利用しやすくなるため、FPGAからSoCの手法に似てくるのである。設計の再利用、IPの再利用をより進めていき、早く出荷できるようにする。

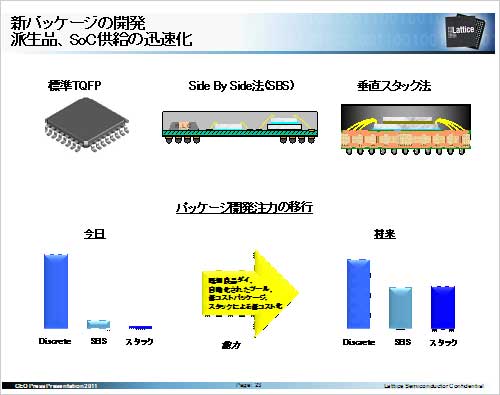

図2 3D IC化をFPGAメーカーの中で先頭で進める 出典:Lattice Semiconductor

パッケージ技術ではハイエンド狙いの大手FPGAメーカーよりもリードしているという。3次元ICでは、良品 (KGD: knowngood die)を持つことが低コストにはマストとなるとBillerbeck氏は言う。すでにFPGAメーカーとしてスタック+ワイヤーボンディングによる3次元 ICを持っていると自慢する。FPGA大手2社はチップを横に並べる擬似3次元あるいは2.5次元ICしか持っていないという。今後はスタックをさらに増やし、低コスト化小型化を進めていく。

図3 ラティスのプラットフォーム戦略でコストを削減 出典:Lattice Semiconductor

同社は製品のシリーズを揃えているだけではない。プラットフォームマネージャーと呼ぶ2チップ技術を持ち、アナログのパワーマネージメントICと、FPGAのデジタルチップを1パッケージ内に収めている。ノイズの問題などを避け、パワーマネージメントICとしても単なるDC-DCコンバータだけではなく、ホットスワップ制御や、電源のシーケンス制御、電圧モニタリングなどの機能も持っている。このプラットフォームマネージャー技術が2チップソリューションを支えている。こういった設計手法、パッケージング、プラットフォームといった技術を推進するのはインテルから参加したベテランのエンジニアたちだという。

最後に、最近注目を集めているTabula社についてたずねてみると、「(同社の)技術に関心はあるものの、競争相手はザイリンクスやアルテラであり、当社ではない」として、ローエンド、ミッドレンジに集中するラティスとは戦略の違いが明確に出ている。

参考資料

1. 2極化するFPGA業界、低電力、小規模市場にラティスやシリコンブルーが活躍 (2011/04/28)