ナノインプリントの量産化は22nm以降のNANDフラッシュ、ハードディスクから

Mark Melliar-Smith氏、米Molecular Imprints社CEO

2001年、米国テキサス州オースチンで創業したMolecular Imprints社が、22nm以降のリソグラフィ技術であるナノインプリント装置を開発、まだ試作用であるが大手数社に納入した。22nmとなると従来の延長技術のダブルパターニング、あるいはEUV(13.5nmの超短波長)リソグラフィが候補に上がっている。ダブルパターニングはスループットが半分、EUVは光源、マスクなど未解決の問題を抱えている。ナノインプリントは割り込めるか。来日したMolecular Imprints社CEOのMark Melliar-Smith氏に勝算を聞いた。

Q(セミコンポータル編集長 津田建二):今回来日した目的と、ナノインプリント技術の現状を教えてください。

A(Molecular Imprints社CEOのMark Melliar-Smith氏):試作用の装置を最近ではSEMATECHに納入し、その前に東芝にも納入しました。東芝は2008年2月に行われたSPIE Advanced Lithography 2008で22nmのパターンを形成したことを発表しています。今回の来日は、日本に潜在的な顧客がいるからです。後ほど述べますが、東芝以外でも潜在顧客はハードディスク装置を作っている日立や富士通などです。

できるだけSiプロセスに沿った技術を利用

Q:ナノインプリントのアイデアは数年前からありますが、なかなか見通しが立ちません。これまでのアイデアと比べた特長は何ですか?

A:これまではみんな独自のやり方で、ナノインプリント技術をやろうとしてきました。しかし当社はできるだけ半導体プロセスと互換性を保つ方法でこの技術を確立しようとしています。ここが大きな違いです。

作り方は非常に簡単です。まず透明なガラスマスクに凹凸のパターンを描きます。このガラスは半導体のフォトマスクと同じ材料で構成されますが、凹凸のパターンをエッチングで作ることだけが異なります。この凹凸パターンを作るのは、大日本印刷や凸版印刷、HOYAなどマスクメーカーです。これは通常の電子ビーム露光で作ります。

このあとGDSフォーマットに準拠した半導体回路パターンをシリコンウェーハ上に形成します。インクジェット技術を使い液状の光硬化樹脂をこの回路パターンに沿ってたらしていきます。インクジェットは1000ものノズルから一斉に液状樹脂を吐出します。ここでは常温で作業できます。その後、透明なガラスの上(凹凸パターンのない面)からi線の紫外線を照射し、樹脂を硬化させます。樹脂の硬化はフォトレジストと全く同じです。

ガラスの大きさは、ステッパのフィールドサイズと同じ26mm×33mmですので、ウェーハ全面に渡ってこの作業をステップ&リピート方式で繰り返します。ステッパと同じやり方ですが、大きなレンズも要りませんし、真空も要りません。レーザー光源も化学増幅レジストも要りません。

出来上がったパターンはフォトレジストと同様、2:1のアスペクト比を持ちます。このあと従来の半導体プロセスと同様にエッチングし、所望のパターンを描きます。

この技術を使って5nmCMOSトランジスタの動作を確認しました。CMOSプロセスと同じようにトランジスタを作り、動作を確認できたということは、半導体プロセスの微細化は少なくとも5nmまでは可能だということです。

22nm以降のNANDフラッシュとハードディスク市場に参入

Q:狙う市場はどこですか?

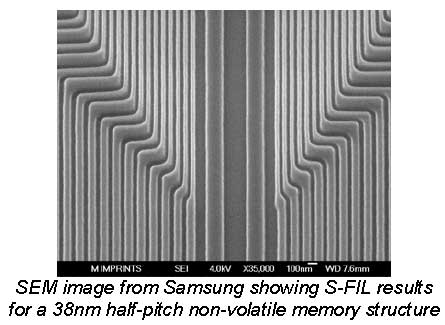

A:当社は光リソグラフィやEUVリソグラフィに替わる可能性を求めてナノインプリント技術を開発しています。狙う市場は半導体メモリーとハードディスクです。半導体は微細化を推進するNANDフラッシュやDRAMなどのメモリーです。サムスンは、ハーフピッチ38nmのフラッシュメモリー構造に使ってみた実験写真を発表しており、直角に曲がる配線パターンでもコーナー部での問題が全くありません。波長を使わないため、OPC(光近接補正)を使わなくて済みます。

また、ハードディスクはこれまでのパターンなしから複数のビットをパターニングする方向へと変わります。最近は高密度化のため垂直磁気方式を採用しており、さらに高密度化するためにビットのパターニングにナノインプリントを使います。日本では日立グローバルストレージシステムズや山形富士通などがハードドライブを作っており、それに対応したディスクも製作しています。ハードディスクは1年間に10億枚生産している巨大な市場です。これまで当社はHDD用のナノインプリント装置を10台受注し、そのうち6台を出荷しました。

Q:CMOS LSIの開発に関して、EUVや光リソグラフィと比べて有利な特長は何ですか?

A:この技術、S-FIL(Step and Flash Imprint Lithography)は10nm以下のデバイスでも作製可能です。実際、5nmのCMOSトランジスタをこの技術で作り、動作を確認したという発表がありました。また、既存のCMOSプロセスでそのまま製造でき、193nmリソグラフィとミックス&マッチ技術でCMOSLSIを製造できます。光硬化樹脂を使いますので露光が必要ですが、ダブルパターニング技術とは違い1回露光ですみますので、簡単でCoO(コストオブオーナーシップ;運転稼働コスト)が安いという特長があります。

また、光の波長を使いませんので、デザインルールには関係なく加工できます。さらに、既存の光リソグラフィのインフラ(マスクやレジスト、光源)をそのまま利用できます。

45nmプロセスを1として、22nmプロセスのCoOをナノインプリント技術とEUV、ダブルパターニングで1レイヤー当たりのリソコストを比較した例があります。22nmになるとダブルパターニングは3倍になり、EUVは2.2倍になります。EUVは1台100億円になるとの予測もあります。ナノインプリントだとシングルモジュールでも1.4倍程度、スループットを上げるためリソチャンバを複数台集めたクラスタツールにすると1.2倍程度にしか上がりません。

Q:ナノインプリント技術で微細パターンを作った例はありますか?

A:実際にこの装置を使いまして、東芝は最小寸法18nmのナノインプリントパターンを描いたことを2008年2月に開催されたSPIE Advanced Lithography 2008で発表しています。サムスンは、38nmのNANDフラッシュメモリーに適用し、配線を90度折り曲げたパターンがきれいに形成されている写真を示しています。IBMもストレージ用の不揮発性メモリー用FINFETを作製しています。ここでは20nmと30nmのFINFETをArFおよびKrFレーザーリソグラフィとのミックス&マッチ方式を利用しています。

ハードディスクのパターニングはステップ&リピートではなく、一括露光ですがこの方式でもハーフピッチ24nmの直線パターン、ハーフピッチ28nmのドットパターンを描いた例があります。

Q:パターンを作るための透明なガラスマスクは何回、繰り返し使えますか?

A:マスクは溶融シリカ製です。これは水晶とおなじくらい丈夫ですから、摩耗することはほとんどなく、数百万回使えます。ただし、数千回に一度クリーニングは必要です。

Q:今後のロードマップについて教えてください。

A:最近、オールバニー(ニューヨーク州)のSEMATECHに納入しました。今、32nm以下のデバイス開発に向け300mmウェーハ対応装置であるImprio 300の受注を始めています。これはまだ試作用の装置でスループットは4枚/時とまだ少ないですが、2009年には20nmまでのプロセス開発に向けImprio 3xxを導入します。2010年には最初の量産対応として15nmプロセス対応機でスループットを20枚/時に上げたHVMを出す予定です。2011年の後半には最小寸法7nm、スループット80枚/時の4ヘッド方式のクラスタツールHVM クラスタを出していく予定です。

さらに将来はハードディスク以外にもフォト結晶向けに光を閉じ込めるLEDや、ウィルスと同じサイズのDNAを捉えるためのバイオテクノロジ用途などにも応用できると見ています。