LSI設計を知り尽くしたベテラン達が昨年起こしたインドのデザインハウス

Naveen Chava氏 SiCon社ビジネス開発マネージャー

Srikar Vempati氏 同オペレーションディレクタ

「SoCの設計はお任せください。米国帰りの設計エンジニアから、バンガロールの外資系企業で設計経験を積んだエンジニアまで豊富にいて、なおかつインドを本拠地とするため低コストでSoC設計ができます」。このほど来日したインドのデザインハウス、シーコン社(SiCon Design Technologies)の経営陣にその狙いを聞いた。

図1 SiCon社ビジネス開発マネージャーのNaveen Chava氏(左)と、オペレーションディレクタのSrikar Vempati氏(右)

Q(セミコンポータル編集長):まず会社を設立した経緯を教えてください。

A (シーコン社ビジネス開発マネージャーのNaveen Chava氏):私は米テキサス・インスツルメンツ(TI)で10年間、LSI設計に携わり、その後インドのバンガロールに戻ってからも5年間、TIインドで設計経験を積んできました。オペレーションディレクタのSpikar Vempati氏は米AMDでグラフィックチップに携わり、その前はフリースケールでCPUとグラフィックスプロセッサを融合したFusionプロセッサの開発に従事していました。

その後、2010年8月にシーコン社を立ち上げました。この会社はSiConと書いて「シーコン」と発音します。Silicon Consultingを縮めた言葉です。シリコンSiをベースにしたLSI設計を請け負うことから社名を決めました。起業する上で大事なことの一つは、マネージャーとしての経験です。私たちは共に、米国の半導体企業でマネージャーを経験していたため、SoCのデザインハウスを経営する場合のマネージメントの蓄積があったといえます。

私たち以外にも、エンジニアは海外からの帰国組やインド国内でも外資系企業でLSI設計を手掛けていたベテランエンジニアが揃っています。海外経験者の多いデザインハウスの「売り」は何と言っても設計が高品質であると同時に、インドゆえの低価格です。

Q:もう顧客を獲得されましたか。

A:当社の顧客には、早くもARMやブロードコム、マーベル、NXP、TI、サイプレス、STエリクソンなどがいます。しかし、日本に関係する企業はルネサス・モバイルのみで、日本の総合電機メーカーや大手半導体IDMなどはまだ顧客にいません。私たちは日本の半導体メーカーとセットメーカーに使っていただきたいのです。ルネサスとノキアとの合弁会社であるルネサス・モバイルを顧客にできたのはルネサス・モバイル・インドから受注したためです。日本企業との直接的な取引を今後、構築していきビジネスを拡大することが当社の目標です。

Q:シーコン社はどのような範囲のLSI設計を扱いますか。

Q:当社がカバーするVLSI設計の範囲は、RTL(register transfer level)工程から、マスクを出力するGDS II形式の出力まで、とVLSI設計の全工程に渡ります。顧客からはRTLだけでいいとか、検証(verification)まで頼むとか、レイアウトや配線だけに特化してくれとか、あるいはDFM(design for manufacturing)だけ、といったさまざまな要望が来ますが、どの段階でも応えられます。しかも、DFT(design for testing)後に論理設計にタイミング設計までも考慮した設計手法タイミングクロージャーも含みます。また、デジタル回路だけではありません。アナログ回路、例えばAD/DAコンバータや高速インターフェース回路、無線のNFC(near field communication)回路など高速から低速、低消費電力まで手掛けています。

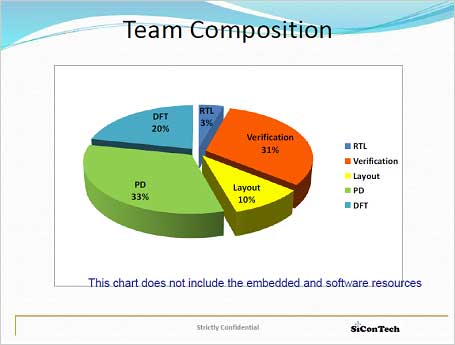

図2 SiCon社のデザインエンジニア構成

Q: 他のデザインハウスと比べて有利な点は何ですか。

A: 当社の強みは、VLSI設計のさまざまなレベルを扱う場合に、システムアーキテクチャの観点から設計する、ということです。システム全体を鳥瞰し、チップ上のCPU、GPU(グラフィックプロセッサユニット)、DSP(デジタルシグナルプロセッサ)を見ながら、設計仕様をアタマに描き、バスがボトルネックになっている場合にはバスアーキテクチャまで手を入れることもあります。先ほども述べましたが、インターフェース回路の設計にはアナログ設計も必要です。アナログのスキルを生かせます。プロセス技術に対しても最先端の28nmからこなれた180nmのチップまで扱っています。

デザインハウスとして言うまでもありませんが、EDAツールの扱いはもちろん習熟しています。メンターやケイデンス、シノプシス、マグマなどほとんどのツールを使いこなします。

IPレベルでは、ARMプロセッサに加え、DDR2/3、DSPコア、ミクストシグナルや高周波回路(RF)などのIPもシリコンに焼き付けてタイミング動作も含めて使えることを実証しています。

チップの信頼性に影響を及ぼすホットキャリヤ寿命や、NBTI(逆バイアス温度経時変化)などの信頼性評価も含み、サブスレッショルドノイズやIRドロップのパッケージレベルでの動作解析までも行います。

Q:これまで設計した、あるいは設計中の例を差し支えない範囲で教えてください。

A:すでに設計を終えテープアウトしたVLSIとしては、28nm/45nm/65nmのモバイルベースバンドチップやアプリケーションプロセッサ、32nm/45nmの高速x86プロセッサやGPUなどがあります。ここでは、オーディオやビデオ、ディスプレイや画像、グラフィックス、カメラという回路ブロックや、USB3.0やHDMIなどの高速インターフェース、MIPI(Mobile Industry Processor Interface)トランシーバなどのミクストシグナル回路の物理設計も扱うLSIです。低消費電力のために電源電圧をアダプティブに動かすAVS方式や、ダイナミックに電圧や周波数を変えるDVFS方式も導入してLSIを設計しています。

CPUコアの部分では、ARM9/11といったなじみ深いCPUだけではなく 比較的新しいCortex-A9ベースのIPコアをシリコンに載せるための設計も手掛けています。ネットワーク機器用途では、ギガビット/秒のスイッチ、ルーターやプロセッサなども設計しています。

こういったプロセスはTSMCやグローバルファウンドリーズなどのファウンドリメーカーに製造依頼しています。

Q:シーコン社のスキルを活用するとVLSIはどのくらいの期間で設計できますか。

A:顧客の要求、仕様、RTL、ネットリストのレベルなどによって違いますが、ざくっと言ってそれぞれ3ヵ月くらいかかります。また、プロセス技術によっても異なります。90nm、65nmを1とすると、40nmはプラス1カ月、32nmはプラス2ヵ月、28nmはプラス3ヵ月、22nmだとプラス6ヵ月余計にかかると見積もっています。さらに顧客の要求しだいですが、性能/バンド幅の向上や、消費電力の削減、チップ面積の15%削減、リーク電流削減などの要求も加われば2〜6ヵ月余計にかかると見ています。

トータルのVLSIを大ざっぱに見積もると、アナログやSRAM部分も含む5000万ゲートのSoCだと、要求から生産立ち上げまで2年くらいかかります。また、同じSoCでもネットリストが確定してからGDS IIまでだと6ヵ月、RTLからGDS IIまでなら1年くらいと見積もっています。

Q:開発しているLSIからは、応用として携帯機器が多いのでしょうか。

A:今手掛けているアプリケーションとしては、タブレットやスマートフォン、あるいはそれらを利用した新しいPOS端末、2〜3インチのプリンタなどがあります。電子投票機を設計したこともあります。組み込みシステムになると、例えばトラステッドコンピュータボードにはデータセキュリティも組み込むことになりますが、チップ設計だけではなく、PCBボードレベルやソフトウエア(ファームウエア)までも組み込みます。

Q:今回、日本に来て、日本市場をどのように見えますか。

A:日本のメーカーを回って、当社の技術レベルが高いことや、当社のコミットメントと専門技術を日本のメーカーに理解していただきました。私たちは日本の顧客をよく理解できましたし、私たちも好感を持たれていると感じました。

日本市場は円高によって輸出産業が痛めつけられているように思えます。しかし、市場が回復すれば、日本のメーカーは当社の強力な顧客にきっとなると信じています。