LEAPの成果報告、どう活用するか、問われる参加企業

超低電圧デバイス技術研究組合(LEAP)のプロジェクト「低炭素社会を実現する超低電圧デバイスプロジェクト」は平成22年度から本年度までの5年間に渡って研究されてきた。LEAPが主催する「第4回 低炭素社会を実現する超低電圧デバイスプロジェクト成果報告会」がこのほど開かれ、その開発されたデバイスが披露された。

図1 LEAPが主催した成果報告会

トランジスタとメモリの取り組み

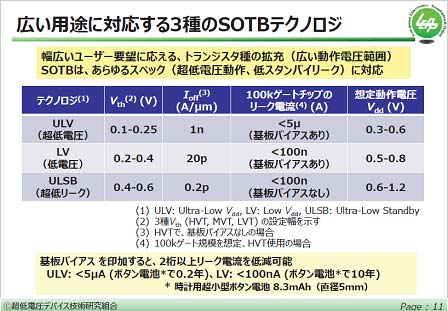

LEAPが5年間取り組んできたテーマは五つ。SOTB-CMOSと呼ぶトランジスタ構造、STT-MRAM、PCメモリ、原子移動型スイッチデバイス、そしてナノカーボン配線である。SOTB-CMOSは、CMOSトランジスタのチャネル領域にノンドープ層を設け、ゲートしきい電圧Vthのバラつきを減らし、かつSOIウェーハによって空乏層を上下からはさみリーク電流を減らす構造を採った。バラつきを抑えることで、電源電圧を下げることができる。例えば0.2〜0.4Vのしきい電圧で、0.5〜0.8Vの動作電圧を想定し、10万ゲートの規模のチップで100nA以下のリーク電流を達成している(図2)。さらに、中性子線によるソフトエラーにもバルクに比べ3けた強いことを確認している。

図2 SOI CMOSにノンドープ層を設けたSOTB(Silicon on Thin Buried Oxide)トランジスタの性能 出典:LEAP

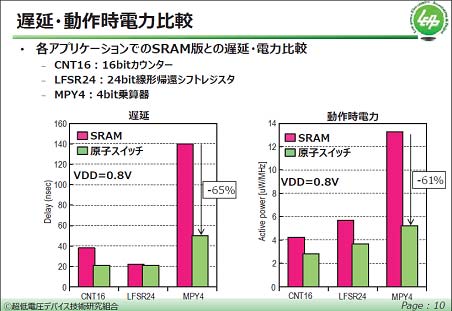

原子移動スイッチでは、FPGAなどのロジックセルの切り替えスイッチとして使うことを狙っており、従来FPGAのスイッチに使われているSRAMを原子移動スイッチと置き換えたチップを作り比較した。従来SRAMプロセス、原子移動スイッチプロセスとも65nmの1層ポリシリコン、7層メタル層の多層配線のCMOS技術を使用した。1セル当たり2×4入力のLUT(ルックアップテーブル)のセル面積を比較すると、原子移動スイッチはSRAMベースの1/4となった。

またいくつかのSRAM基本回路を試作し、SRAMと原子移動スイッチとの性能も比較した。16ビットカウンタでは遅延時間は半減、4ビット乗算器では1/3に減った(図3)。ただし、24ビットの線形帰還シフトレジスタではほとんど変わらなかった。動作電力も比較した。16ビットカウンタと24ビット線形帰還シフトレジスタでは動作時電力は共に2/3程度減り、4ビット乗算器では1/3に減った。共に電源電圧は0.8V。原子移動スイッチに向くRTLの論理合成・マッピングツールも作成している。原子移動スイッチはCMOSプロセスの多層配線部分に設けるため、プロセス上のなじみは良いようだ。

図3 従来のSRAMベースの基本回路と、原子移動スイッチベースのそれとの比較 出典:LEAP

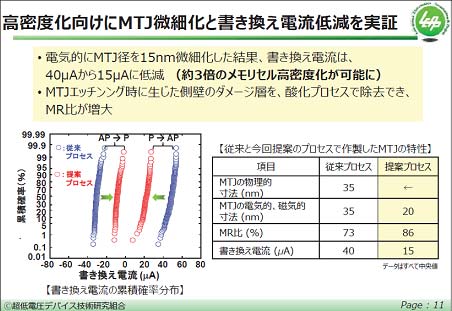

STT-MRAMでは、微細化するとMTJ(磁気トンネル接合)の寸法バラつきが大きくなるという問題があった。そこで接合の周囲の側壁を酸化することで実際の接合の直径を微細にした。すると、バラつきが減少した。そこでリソグラフィによる物理寸法は35nmと従来と同じに加工しながらもMTJの電気的・時期的寸法を35µmから20µmに微細化すると、書き換え電流が従来の40µAから15µAに低減した(図4)。側壁酸化にスパッタと自然酸化を併用することで、リーク電流成分も消えたとしている。

図4 微細化してもバラつきは増加せず消費電流も下がった 出典:LEAP

16Kビットのメモリアレイも試作した。抵抗バラつき3σは目標の16%以下をクリヤーした。マクロ評価用に1Mビットアレイも試作している。書き換え回数の加速試験ではストレス電圧を0.9Vから0.8V、0.7Vと加え、0.65Vでは10の16乗という回数を見積もっている。MTJはさらに磁気センサとしても動作できるため、メモリだけではない応用研究も進めている。

実用化に向けた問題解決へ

相変化メモリRAMでは、ANDフラッシュ並みの小さなセル面積でありながら、従来のPRAMよりも低消費電力動作ができるTRAMを開発中だ。PRAMではSb、Te、Geの合金の結晶と非晶質のスイッチングによって変わる抵抗を利用したが、TRAMでは結晶Aから結晶Bへの遷移を利用するため、消費電力が低いうえに高速の動作が可能だ。GeTe膜とSb2Te3膜を交互に何層も重ね合わせる「超格子」を作る。その結果、従来のPRAMと比べ、電源電圧は40%に下がり、消費電流は半減した。1M/2Mのマクロを試作し動作を確認しているが、剥離による高抵抗不良が発生しており、これを解決する必要がある。

最後にナノカーボン配線だが、要求は二つある。一つは、Cu配線を微細化すると配線のシート抵抗が急増していく問題を解決できること。もう一つは、3次元NANDフラッシュのように高いアスペクト比の導通配線が求められることだ。コンタクトホールやTSVを埋めるのにナノカーボンが向く。横方向の配線には多層グラフェンを使い、縦方向の配線にはCNT(カーボンナノチューブ)を使い分けする。ナノカーボン配線密度がまだ低いが、300mmウェーハに形成するという実験を行った。

これらの成果を出資会社が生産ラインに載せることができると、新たに製品開発するよりもコストを抑えられる。もちろん、しっかりしたマーケティングが重要で、顧客開拓をエンジニアが自ら行わなければならない。そのための投資も必要だが、他の製品開発でも同様な投資がかかると考えるのなら、結局、活用する方がROIは有利ではないだろうか。