次世代TFET、共鳴TFET、finFET対FDSOIなど新デバイスが集まったIEDM2013

IEEE IEDM(International Electron Device Meeting)では、トンネルFET(TFET)をはじめとする次世代半導体の発表がさまざまな研究所、大学、企業からあった。TFETにはサブスレッショルド電流の傾斜を急峻にできるというメリットがあるため、各社はこれを生かし、5nmノードを狙い、0.5V以下の電源電圧を狙う。

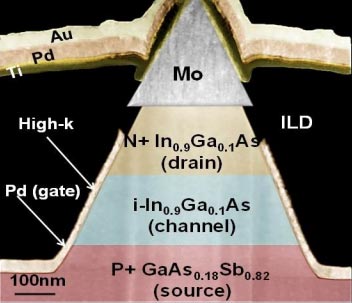

米Pennsylvania State Universityと米NIST(全米標準技術研究所)、英IQEは、エネルギーギャップを崩すようなTFETについて述べた。このトランジスタは、人体に埋め込むことのできる医療デバイス用に開発された。エネルギーギャップは、ほぼゼロあるいはブロークンギャップに近いとしている。電子がバリアを突き抜けトンネリングしやすくするためだ。このTFETは縦方向に電流を流す構造だが、端子は全て表面から取り出せるようにしている(図1)。InGaAs/GaAsSb系のIII-V族トランジスタをベースとしている。チャネル長200nmのブロークンギャップTFETは、740µA/µmと高い駆動電流を得ている。RF相互コンダクタンスは700µS/cmと高く、遮断周波数はVDS=0.5Vで19GHzである。

図1 縦型TFETのTEM(透過型電子顕微鏡)写真 出典: Suman Datta氏、Pennsylvania State University

「このトランジスタは当研究所で開発した。ロジックLSI用のMOSFETを置き換え、消費電力の問題を解決しようという狙いである。今回の試作で高周波応用の可能性が一歩進んだと見ている。人体に埋め込む用途でデータを処理し送信するといった低消費電力の応用に使いやすくなる」とPennsylvania大の大学院生のBijesh Rajamohanan氏は同大のウェブサイトで述べている。

もう1件、IEDMでの目玉は、Intelが共鳴トンネルFET(R-TFET)を発表したことだ。このデバイスのサブスレッショルド電流の傾きは、3桁の電流範囲に渡って25mV/桁と急峻である。これによってゲート長が9nmを切るTFETにスケーリングできるとする。

このR-TFETは、Intelのダブルゲートヘテロ接合TFETと同様の材料の組み合わせを使う。「nチャンネルTFETのソース領域に伝導帯の低いエッジを持つ材料がある。このバンドの配列によって、狭い三角ポテンシャル井戸がヘテロ接合のソースエッジに出来る。この井戸型ポテンシャルは離散的な共鳴エネルギー準位を持つ。半古典的な見方をするなら、この設計はトンネリングするための実効的なバンドギャップが増えるので、TFETの駆動電流を下げることになる」とIntelの研究者であるUygar Avci氏とIan Young氏は言う。

「この共鳴エネルギー準位がソースの価電子帯レベルに一致したときだけ、デバイスはオンする。このため、オンとオフの領域間をトンネルする割合が高速に変化する。この結果、R-TFETは、ヘテロ接合TFETよりも急峻なサブスレッショルド電流が得られるという訳だ」と述べている。

自己組織化ReRAM

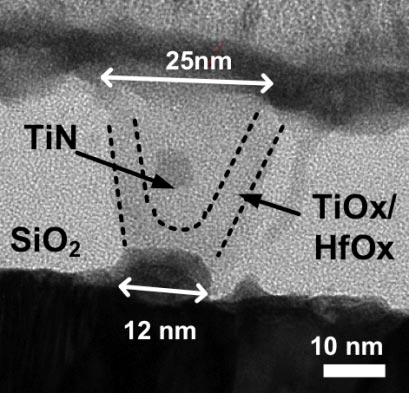

抵抗変化メモリReRAMはフラッシュメモリを置き換えようとして開発が活発だ。NANDフラッシュと比べ書き換え時間が短く、書き換え回数も多いと言われている。IEDMでは、多くのReRAMの発表があった。中でもStanford大学はメタル-酸化膜ReRAMデバイスについて発表した。このメモリは、ジブロック共重合体による自己組織化プロセスを使って製造されている。このパターニング技術を使えば、このメモリデバイスを12nm以下に比例縮小できる。2層のTiOx/HfOxデバイス(図2)を試作し、2.5Vで書き込み、もっと低い電圧でスイッチング動作させ、10の7乗回の書き換え回数を得ている。スイッチング速度は50nsとしている。

図2 DSAプロセスで作製されたReRAMデバイス 出典:Stranford University

Stanford大の自己組織化プロセスでは、ジブロック共重合体のPS-b-PMMAは、プロピレングリコールメチルエーテルアセテートに溶ける。試料を窒素雰囲気中、185℃で12時間アニールすると自己組織化しやくなる、と同大は述べている。この後、試料をDUV(遠紫外光)で10分間露光し、氷酢酸に20分間浸す。PMMA成分を選択的に除去することで、直径20nmの穴が並んだこのPSテンプレートが得られる。このPSテンプレートはエッチング用のマスクになるという。「ジブロック共重合体による自己組織化プロセスは、従来のリソグラフィ技術よりももっと効率よく、安価にナノスケールのチップを製造できるだろう」とStanford大学電気工学科のH.-S. Philip Wong教授は同大のウェブサイトで述べている。

FinFET対FD-SOI

Intel以外の大手半導体メーカーは、20nm以降のロジックノードではさまざまなオプションを調べている。16nm/14nmノードでは、少なくとも二つの大きな選択肢がある。finFETか、FD-SOI(Fully depleted silicon on insulator)プレーナMOSFETか、いずれかだ。IEDMでは、TSMCが16nmのfinFETプロセスについて初めて述べた。STMicroelectronicsとCEA-Leti、ルネサス、GlobalFoundries、SoitecはFD-SOIに関する発表を行った。これは14nmノード以降に向けたゲート長20nmのデバイスである。

その一部として、TSMCの16nm finFET技術では、0.07平方ミクロンのSRAMとCu/low-k配線、high-kメタルゲートなど、モバイルSoCへの応用を視野に入れている。TSMCによると、このトランジスタは、30mV/V未満のDIBLで短チャンネル効果を抑え、nMOS/pMOSとも、0.75Vで520/525µA/µmのドレイン電流Idsatを持ち、オフ電流Ioffは30pA/µmという特性を持つ。

Finのパターニングと48nm finピッチのバルクCMOSは、ピッチ・スプリッティングというリソグラフィ技術を使って製造したという。このパターニング技術で64nmのメタルピッチを可能にした。

FD-SOIに関しては、STMicroelectronicsなどが20nmゲートと25nm厚のBOX酸化膜を使ったUTBB(ultra-thin body and box)デバイスを発表した。この技術は、nチャンネルMOSにはシリコン、pチャンネルMOSにはSiGeチャンネルを利用するデュアルチャンネルFETが特長だとしている。実効電流IeffはnMOS/pMOSでそれぞれ630/670µA/µm、オフ電流IoffはVdd0.9Vで100nA/µm。「チャンネルに歪みを導入し、RDSエピタキシーと接合深さを最適化することで、高性能な第2世代のUTBBデバイスを開発できた。これにより14nmへスケーリングできる」とSTMicroelectronicsのQing Liuシニアスタッフエンジニアは語っている。

Mark LaPedus, Semiconductor Engineering (http://semiengineering.com/)