大手顧客から注文を打ち切られても、新製品で成長を伸ばすSilego社

大手の顧客から注文を打ち切られたらどうするか?Intel向けのチップを開発してきた小さなベンチャー、Silego社は、4年前クロックタイミングチップの注文停止を告げられた。にもかかわらず、しぶとくしかも成長に変えてきた。CEOのIlbok Lee氏は、自分の名前はIlb OKと読めばOKなのだから、新たな技術を開発すればいい、と常に前向きだ。

図1 Silego社CEOのIlbok Lee氏

2001年創業のファブレスであるSilego(シレゴと読む)は、クロックタイミングICを設計、Intelに納めることで急成長してきたが、2007年ころからクロックICビジネスは頭打ちになってきた。IntelはIvy Bridgeなどのプロセッサやその周辺を含めたチップセットの中にクロックICを集積してしまったのである。クロックICを内蔵したためにSilegoのチップは不要になった。

現実に2007年から2010年くらいまでは、Intelも従来製品の生産を続けなければならないため、事業はキープできた(図2)。しかし成長はしない。そしてそのあとは生産中止に追い込まれ、クロックICは極めて少なくなった。このため、新たなビジネスを立ち上げなければなかった。

図2 プログラマブルアナログを急成長させたSilego社 出典:Silego Technology

そこで、目を付けたのは、プログラマブルアナログICである。クロックタイミングICの用途はデジタル回路だが、その設計技術はアナログである。これまでの技術資産を生かそうとしたわけだ。同社は、新しい技術をCMIC(Configurable Mixed Signal IC)と呼んだが、果たして市場はあるか。

狙った市場は、従来ならディスクリートで回路を組まなければならなかったI/O周りやちょっとした周辺回路の受動部品とディスクリートトランジスタ、標準ロジックなどの1チップ化である。こういった回路はプリント基板全体から見れば小さいとはいえ、数cm角はある。この回路を1〜2mm角の1チップに集積するのである。数cm角が1〜2mm角くらいに小さくなる。

この発想は当たった。スマートフォンに売れた。スマホの最大の問題はバッテリ寿命を延ばすことである。アプリケーションプロセッサには機能を増やしてため、消費電力はどうしても増えてしまう。スマホの設計者は少しでもバッテリを大きくしたいが、場所がない。このためプリント基板を「コの字」にするなど、わずかな面積だけで済ませるように基板設計に注力してきた。ここにSilegoのチップを使えば基板面積が数cm角分は減る。この分、バッテリを大きくして寿命を延ばせる。

案の定、図2にある通り、2010年までは従来のクロックICビジネスが継続していたが、2009年からCMICビジネスを立ち上げ、急速に伸びていった。これに対して従来のクロックICは2010年以降急速に小さくなった。2013年はCMICが9割以上を占めるようになり、会社は急成長を遂げている。

では、このCMICとは何か。基本的には、2010年5月に紹介した通りだが(参考資料1)、当時と異なる点は、開発ソフトを充実させ、CMICの位置づけを明確にしたこと。さらにはロードスイッチ新製品も出したことだ。今回は、従来からあるGPAK Designerソフトウエアツールに、DRC(デザインルールチェッカー)を加えた。同社のFPGAはOTP(One time programmable ROM)ベースであり、最終的にはプログラムする。回路の接続条件やフリップフロップやコンパレータなど標準ロジックはソフトウエアライブラリに入っており、スケマティック入力できるが、今回のDRCの導入によって、描いた設計図を分析、エラーにはフラッグを立て、警告を発する。このソフトの導入によって設計の生産性が上がり、GPAK ICを使って簡単な回路を設計する場合、慣れると20分以内でエラーなく完成できるとしている。

図3 CMICの位置づけ 出典:Silego Technology

CMICの位置づけは、AlteraやXilinxのFPGAと違ってずっと回路規模が小さいこと(図3)。ルックアップテーブル数なら20 LUT程度だという。これに対して、SiBlue(Latticeに買収された)はデジタルが中心で価格も高い。またアンプやコンパレータのようなアナログ機能では、同様にプログラム可能なCypress社のpSoCと違い、マイクロコントローラを使わない。コテコテのハードワイヤード回路だが、アナログ部分を簡単に設計できるツールを備えている点がユニークと言えよう。

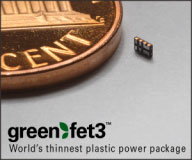

図4 厚さ0.27mmのロードスイッチ 出典:Silego Technology

このほど新製品として、パワーFETをいくつか集積した負荷スイッチSLG59M1446Vもリリースした。これは、わずか1.0mm×1.6mmのパッケージに収容しながら連続1Aの電流を高速にスイッチできるIC。さらに最大6Aと2Aの電流を切り替えられるnチャンネルパワーMOSFET利用の負荷スイッチSLG59M1470Vと、最大2.5Aの電流を切り替えられ、しかも厚さが0.27mmと受動部品と同じ厚さのパッケージLo-Z ETDFNも発表した(図4)。最後のLo-Zパッケージは高さがWLCSPの半分になるため、ウエアラブルエレクトロニクスへの応用も視野に入れている。

参考資料

1. 新しい市場開拓が可能になったFPGA業界、チャンスと脅威が併存(2) (2010/05/19)