TSVの商品化を早める平面配置手法によりFPGAの集積度を上げるザイリンクス

米ザイリンクス社は、シリコンインターポーザ技術を使い、FPGAチップを複数つなぐ新しい高集積化技術を開発したと発表した。3D IC用の技術であるTSV(through silicon via)を使いながら3次元にチップを積み重ねるのではなく、2次元に配置する。縦に積むとTSVホールの配置の制限やインターポーザにおける配線設計の自由度が損なわれるため、現段階では一部のイメジャーを除いて製品化されていない。

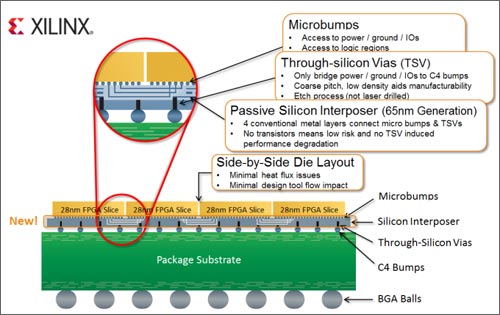

図1 TSVとシリコンインターポーザを使い3D ICの商品化へ第一歩を踏み出す

ザイリンクスがこの技術を発表した場所は台湾である。台湾にはASEという後工程ファウンドリ世界ナンバーワンの企業があり、前工程ナンバーワンのTSMCもある。TSV技術は前工程、後工程のどちら側でもできるプロセスである。それぞれの専業メーカーが台湾にあることは、ユーザーから見ると実にビジネスのやりやすい地域となり、台湾が3D ICの拠点にふさわしい拠点となりうる。

この技術は、FPGAの集積度をムーアの法則と共にさらに上げようとするときに使う技術である。FPGAは最終製品に使うことは稀で、たいていの場合SoCなどの高集積ICを設計する場合の設計のハードウエア検証に使うことが多い。このためチップの専有面積はそれほど問題にならない。今回の技術のように複数のチップを横に並べる方法は3次元化の最短距離にある。

ただし、横に並べるメリットは何か。FPGA製品を1個ずつ並べても同じように見えるが、単体チップを1個ずつ接続するユーザーから見ると、配線工程が非常に複雑になる。高集積のFPGAを隣接させたチップ同士をつなぐ場合には1万もの接続点をデータが走ることになるという。インターポーザからTSVでボール端子を出せばプリント基板メーカーの煩わしさは従来と変わらない。ユーザーにとってはリスク軽減となる。2つのFPGAチップをプリント基板上に並べる場合と比べると、重ねたシリコンでは接続のバンド幅は1W当たり100倍となり、レイテンシは1/50に縮まると同時に、高速のシリアルあるいはパラレルI/Oは使わなくて済む。

ザイリンクスは、この技術を28nmのVirtex-7シリーズのLX2000Tデバイスに適用し、すでに入手可能なソフトウエアサポートツールISE Design Suit 13.1を使ってソフト開発できるとする。この28nmのLX2000Tは、現在最先端の28nmプロセスを使った最大集積度のFPGAと比べてロジック容量は3.5倍以上になり、シリアルトランシーバを集積した高集積の28nmFPGAと比べてもロジック容量は2.8倍にも達するという。

このチップは高集積向けマイクロバンプ技術を使い、TSMCの28nmプロセスで生産する。複数のFPGAをプリント基板に搭載する場合と比べて、消費電力、システムコスト、基板回路の複雑さ、のどれも全て優れているとしている。TSMCのシニアバイスプレジデントであるShang-Yi Chiang氏によると、TSVとシリコンインターポーザを使ってシリコンをその上に搭載する方法は、ザイリンクスにとってリスクが軽減され、量産途上にあるという。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム