日立製作所がMEMS可動部を多層配線に設ける1チップCMOSセンサーを試作

多層配線技術を使い、配線層部分にMEMS可動部を設けるという、1チップ技術が登場した。日立製作所の中央研究所がCMOSプロセスに妥協することなくMEMSを集積できるプロセスを第20回マイクロマシン/MEMS展で発表した。

MEMSチップの利点は可動部分が小さいこと。モノリシックでMEMSセンサーなどの可動部分を作るためにはCMOS回路側でプロセス上の妥協をしなければ作製が難しかった。このため、MEMSセンサーとCMOS ICを無理にモノリシックに集積せず、マルチチップで1パッケージに納めるシステムインパッケージ(SiP)が主流になりつつあった。しかし、複数のチップを横に並べたり、縦に積んだりしてもパッケージのサイズがトータルの大きさを決めていた。

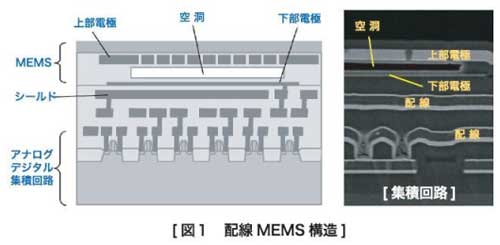

日立製作所はCMOS ICプロセスをほぼそのまま使えるプロセスを開発、多層配線部分にMEMS可動部分を設けることで、1チップMEMSセンサーを開発した。CMOS回路では回路部分を製作した後にダマシンプロセスなどによって多層の配線を形成するわけだが、この多層配線部分にMEMS可動部分を形成してもCMOS回路の性能は変わらない。この技術は、2〜3層の配線層W、WSi材料で形成した後に、厚い絶縁層の一部をくり抜いて空間キャビティを形成するというもの(図1)。

キャビティの形成は次のように行う。まず、下部電極を形成した後、厚いSiO2層を堆積させ、さらに上部電極を形成する。上部電極に多数の穴を開けておき、その上からプラズマエッチングあるいはウェットエッチングなどで上部電極の下のSiO2層を削っていく。電極の穴の大きさとエッチング条件などでキャビティサイズが決まる。削られる個々の穴が次第につながっていき、最終的に広い空洞ができる。キャビティの大きさはエッチング条件と時間で制御するとしている。

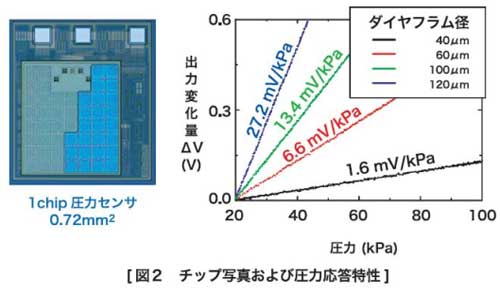

もともと多層配線はプラズマCVDなど450℃以下のプロセスで行うため、MEMS部分を作る工程と多層配線工程との親和性は良い。この空洞を利用して静電容量キャパシタンスの変化によって圧力を検出するという圧力センサーを試作した。図2の例では、50個のダイヤフラムを形成した、0.9mm×0.8mmの小さな圧力センサーであり、ダイヤフラムの直径を変えることでいろいろな圧力変化に対応できる。加えて、検出感度や精度は50個の圧力センサーを組み合わせることで調整できる。

一般的にMEMSなどのセンサー信号はインピーダンスが高いため、ノイズの影響を受けやすいため、センサーからの信号をもっと扱いやすい信号レベルに変換する。そのためのアンプやレベルシフターなどの回路を1チップに集積する。今回は、CMOS回路としてアンプなどアナログ回路だけで構成したが、A-D変換してデジタル信号処理する方法もありうると日立の説明員は答えた。

NEDOの「高集積・複合MEMS製造技術開発事業」の支援を受けて開発した、この技術は自動車のタイヤ圧検知や、衝突検知、血圧計、空調機器などに使えるとしている。また、小型であることを特長としてロボットの指先の接触センサーとしても可能だとしている。さらに、一般のCMOS LSIにおいても、空洞キャビティはLow-k材料として使うこともありえる。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム