nMOSトランジスタのばらつきは不純物だけでは決まらない

65nmロジックプロセス(ハーフピッチでは90nmプロセスに相当するプロセスノードhp90)で100万個のnチャンネル/pチャンネルMOSトランジスタアレイ(両方で200万個)を作り、ゲートしきい電圧Vthのばらつきの原因を突き止めた、と半導体MIRAIプロジェクトが、12月18日茨城県つくば市で開かれた2007年半導体MIRAIプロジェクト成果報告会で発表した。pチャンネルMOSのばらつきは不純物の揺らぎにより、nチャンネルMOSは不純物の揺らぎと別の要因が加わっているとしている。

この実験では、Millennium Research for Advanced Information Technology (MIRAI)プロジェクトが、200mmウェーハの中に26個のTEGチップを作り、各TEGチップには20個のサブチップを作った。20個のサブチップの中に、100万個のトランジスタアレイ部分をnおよびpチャンネル2カ所設けたもので、各100万個のnMOSトランジスタ、100万個のpMOSトランジスタからなる。アレイのトランジスタはnMOS、pMOSともすべて同じ向きに作り込んだ。このような大量のトランジスタアレイを使ってサブスレッショルド電流特性やVthを測定しばらつきを評価した。

100万個のトランジスタについて測定したVthを、累積頻度を示すワイブル分布としてまとめると、きれいな直線状を描き、正規分布していることがまずわかった。しかも、このVthは中央値から±5σ(σは標準偏差)とかなり広い範囲に及んでいる。ただし、その1σはpMOSが43mVであるのに対して、nMOSは65mV、とばらつきはpMOSよりも大きかった。

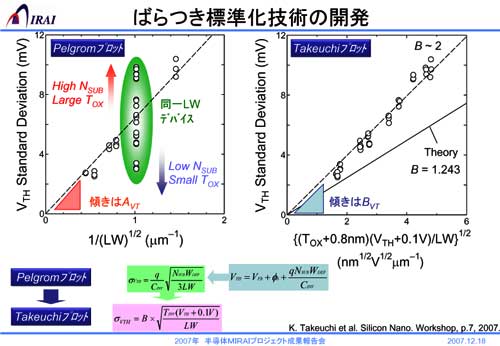

ばらつきの原因を探るため、プロジェクトはVthをノーマライズして表現することを考えた。ノーマライズの手法として、Vthのばらつきσ(標準偏差)とゲート長Lとゲート幅Wで表す方法があるが、これではゲート酸化膜厚や不純物濃度によって直線性が大きく崩れた。そこで、プロジェクトでは、Vthの標準偏差を(Tox+0.8nm)(Vth+0.1V) / LWのルートでプロットしてみると、Vthのばらつきは直線的に表すことができた。

ここで、Toxのゲート酸化膜厚に0.8nmを加えた量はMOS反転を起こした時の実効的な(あるいは電気的な)酸化膜厚を表したものである。また、Vth+0.1Vは、Vthにおけるメタルと半導体との仕事関数の差からなるフラットバンド電圧、および表面ポテンシャルの寄与分-0.1Vを加味したもので、実効的にqNWdep/Coxという式で表わされる(Wdepは空乏層の幅、Coxはゲート酸化膜厚)。つまり、Vthのばらつきへの寄与が不純物濃度のばらつきではないかという仮説のもとに、Vthのばらつき、すなわちσを不純物濃度Nが寄与する式でノーマライズした。

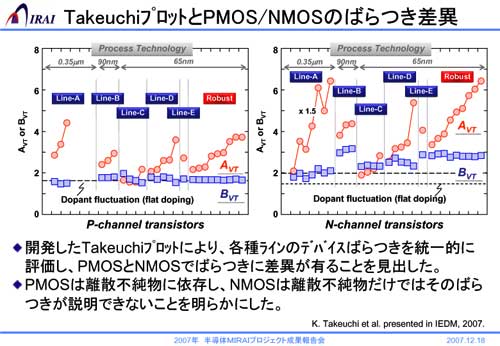

実際には図に示されるように、pMOSとnMOSとで違った結果が得られた。pMOSの場合、不純物濃度が違っても一定であるため、Vthのばらつきは純粋に不純物濃度のばらつきだけで決まることがわかった。しかし、nMOSでは不純物濃度が違ってもその傾きはほぼ一定だが濃度が高くなるにつれ傾きも高くなる傾向があった。このため、Vthのばらつきが不純物濃度だけではなく、他の要素も加わっていると判断した。

プロジェクトでは、フラットバンド電圧、反転層の厚さ、シートチャージ(界面準位や,ゲート絶縁膜中の固定チャージ,界面にパイルアップした不純物原子などの総称)などがあやしいとにらんでいるが、まだ断定するには至っていない。このために酸化膜の厚さのばらつきや界面の荒れ、などを物理的に測定するための技術開発とシミュレーション技術の開発に取り組んでいる。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム